High Precision Low Temperature Drift Modulus Mixed Multichannel ()

1. 简介

1869年,人们通过贝克勒尔发现了第一次放射性现象,20世纪40年代左右,核物理开启了发展的新篇章,众多科学家开始研究一系列科研课题,推动核物理的发展。截止现在,核物理已经成为了高能物理学以及材料学上的一门重要学科,核技术的广泛应用已成为现代化科学技术的标志之一。

目前国内对多道谱仪研发已达几十年,国内众多高校例如清华大学、华中科技大学、成都理工大学已经研发出模拟多道、数字多道等一系列产品 [1]。国外例如cean、ortec等企业也研发出一系列用于处理核信号的多道谱仪产品。但是由于价格高昂,且货期长,后期维护困难,难以大范围的应用在核电站、核废料处理中心以及核安全中心等场所。并且对于不同的环境需要不同通信协议以及添加不同的功能,目前市面上传统多道谱仪难以同时满足这些功能。为了降低成本以及结合模拟多道和数字多道的优势,并且提高自主性,本文设计一款全国产化的模数混合多道。通过将FPGA的高速度、多线程优势和峰值保持器的峰值保持功能结合起来,以此为核心设计出高速可控制的峰值保持电路,使得峰值保持时间实现纳秒级精度可控,有效提升了粒子通过率,降低探测死时间。为了适配多种应用场合例如工业环境、实验室环境以及高辐射环境,本文中的多道系统还将适配多种通信方式,例如USB、RS232和以太网等通信方式。通过长时间的研发调试,此多道谱仪实现了在多种通信方式下使用CeBr3闪烁体光电倍增管探头测试137Cs,分辨率达到4.5%@662 keV。下文将从系统设计、硬件部分、软件部分等介绍本文的研究工作。

2. 系统设计

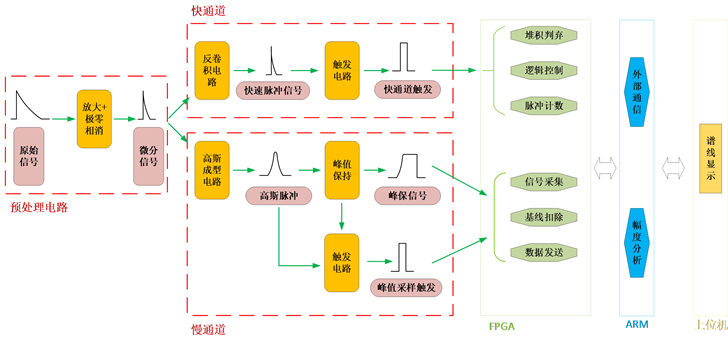

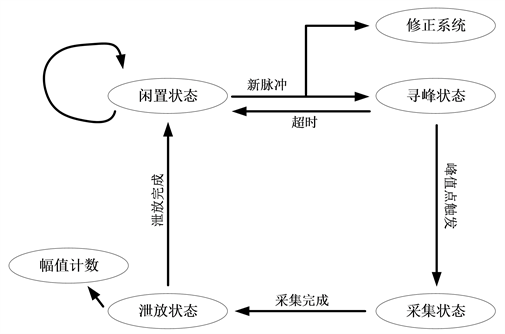

由于模数混合型多道使用的ADC采样速度达不到纯数字多道中高速ADC的采样速度。所以无法直接对电荷灵敏前置放大器输出的原始信号进行准确采样,传统模拟多道使用峰值保持电路来延长放大器输出信号的峰值 [2]。而单纯的峰值保持电路泄放时间太长,难以提高计数率,所以使用FPGA和模拟电路相互配合设计出一种能快速泄放复位的峰值保持电路。如图1为系统工作原理图,下面将介绍模拟部分以及数字部分电路及其逻辑。

图1. 系统工作原理图

本文多道系统工作原理如下:核脉冲事件经由探测器收集并经过前置放大器放大之后会产生如图1中下降沿较长的指数衰减的原始信号 [3]。该信号一般较小,所以需要使用二级放大电路对其进行再次放大,同时,由于普通的CR微分电路在进行微分时往往会使信号出现过冲,因此使用极零相消电路实现基本的成型功能。此后信号将分别进入快、慢通道进行相应的信号成型以及滤波峰值保持。进入快通道的信号将会被反卷积电路成型为脉宽极窄、下降沿极快的指数衰减信号,再通过低延迟高速触发电路将其转换为窄脉冲信号用于触发FPGA。进入慢通道电路的信号首先经过高斯成型电路,输出上升沿、下降沿较长,顶部较为平坦的高斯信号。高斯信号可以减少基线漂移以及弹道亏损的影响,同时降低后端ADC采集电路的采样速度要求 [4]。高斯信号再经过由FPGA控制的峰值保持电路,输出峰值保持信号,峰保信号在与高斯信号经过触发电路输出在峰值点触发的脉冲信号,供FPGA控制ADC进行模数转换。

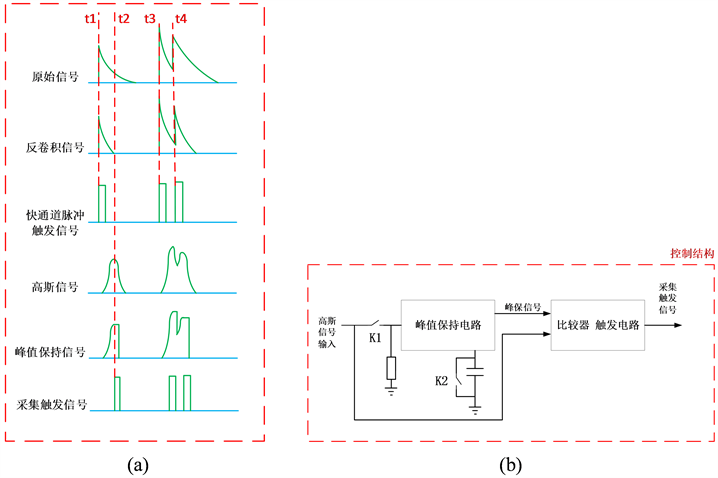

纯模拟的峰值电路泄放恢复时间较长,且稳定度不高,所以本设计采用数字式控制峰值保持电路,利用FPGA的高速处理优势提升整体电路处理速度,并通过内部添加处理算法实现堆积判弃、脉冲计数等功能提高系统分辨率 [4]。峰值保持控制逻辑与电路结构如图2所示:

图2. 逻辑与电路结构图

如图2(b)所示:峰值保持电路控制功能由两个模拟开关K1、K2实现,闲置状态下,K1、K2开关均处于断开状态。峰值保持电路输入端接了一个下拉电阻到地,保持此部分电路的稳定性并降低系统功耗。在t1时刻系统输入一个原始信号,经过预处理电路之后分别输出到快慢通道,由于快通道的反卷积电路功能以及此部分均选用高速芯片,快通道脉冲触发信号几乎也在t1时刻输出。FPGA识别到快通道脉冲触发信号之后,闭合K1开关,使成型之后的高斯信号进入峰值保持电路,并输出峰值保持信号,由于峰值保持电路会保持输入信号的最大值,所以在达到峰值之后的峰保信号与高斯信号在比较器触发电路的作用下,会在t2时刻的峰值点输出采集触发信号。FPGA识别到采集触发信号之后,控制ADC对峰保信号进行采集,即可获得表征能量的电压信号,以此为依据进行谱线测量。同时在t2时刻断开K1开关,防止后续有噪声信号进入影响采集结果。当单次采集完成之后,FPGA闭合K2,将保持电容的电荷泄放,使电路进入闲置状态,等待下一次触发。

在实际测量过程中,如果核脉冲事件产生非常频繁,可能会导致脉冲堆积,例如上图中t3、t4时刻产生的两个堆积脉冲,如果不对其进行处理,就会影响谱线分辨率。在t3时刻被快通道脉冲触发之后,FPGA会生成一个时间节点,同样的在t4时刻被触发时,也会生成一个时间节点,FPGA会比较每两个相邻的快通道触发时间差值。当差值小于单次核脉冲事件信号宽度时,说明发生了堆积,就会将堆积的脉冲丢弃。例如上图中t3和t1的差值大于单次核脉冲事件信号宽度,因此认为t3时刻出现的脉冲有效,而t4时刻和t3时刻的差值小于单次核脉冲事件信号宽度,因此会将t4时刻的采集数据丢弃,但是保留触发计数数据以计算计数率以及通过率。

3. 硬件部分

为了提高多道谱仪性能以及自主性,所选器件全部都为中国大陆内半导体厂商所生产高性能芯片,下文将介绍其中几部分重要电路,例如极零相消、反卷积电路、滤波电路等。

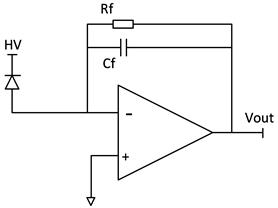

3.1. 极零相消电路

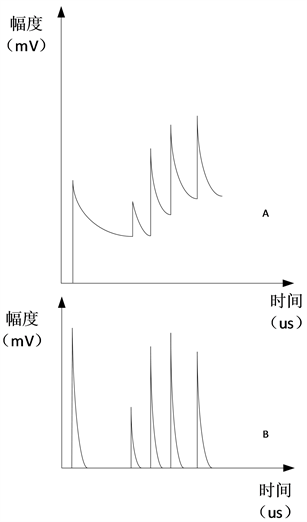

核脉冲信号经探测器转换为电流脉冲之后再由前置放大器放大,一般整个指数衰减信号沿τƒ = Rƒ * Cƒ很长(见下图3所示),甚至可达到数百μs,如此长的衰减时间长度很容易导致信号堆积,影响影响幅值,使得谱线失真 [5]。所以需要使用微分电路对原始信号进行滤波,将其转化为如图4时间较短的脉冲信号,消除指数衰减沿对后续信号的影响 [6]。

图3. 前置放大器原理图

图4. 信号示意图

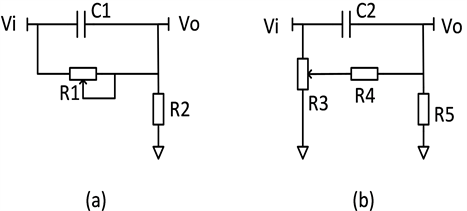

若使用传统的白化滤波器CR进行处理,信号输出常伴有下冲,下冲会严重影响系统对于正常信号的放大性能,大信号造成的下冲会使得放大器过载,使得系统工作于非线性区间,影响分辨率 [7]。所以需要使用极零相消电路,如下图5所示。

图5. 极零相消电路

由于各类前置放大器Rƒ和Cƒ都有所区别,为了获得更好的性能,常需要对极零相消的电路零点进行调节,对于图5中(a)电路而言,选取合适的值,使得

,

,调节R1使得

,并且R2

R1,就可以使用脉宽变窄的同时消除下冲 [8]。

对于图5中(b)电路一般R4比较大、R3较小,设R3电位器接地部分阻值为kR3 (k < 1),通过R4中的电流远小于R3中的电流,因此可以认为滑动变阻器抽动的电压约等于k * Vi。带入传递函数计算其

,

,若将滑动变阻器调节至最上端,既k = 1,(b)电路和(a)

电路相同,若将滑动变阻器调节至最下端,既k = 0,该电路转换为普通的白化CR电路,可用于τƒ无限大的复位型电荷灵敏前置放大器 [9]。基于适配更多的前放类型,本系统采用(b)电路设计。

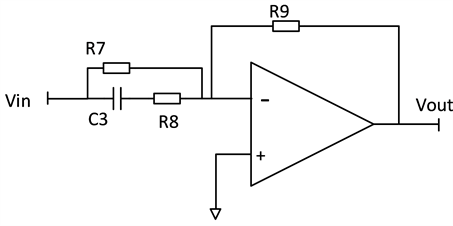

3.2. 反卷积电路

核信号由探测器电离之后,是极快的电流脉冲,但是被前置放大器放大之后,信号沿被拉的很长,就算经过极零相消依然比较长,而用作触发FPGA控制信号的快通道脉冲必须要保证上升时间快和脉冲宽度短,因此设计反卷积电路(图6)从放大信号中还原出快速的脉冲信号。

图6. 反卷积电路

反褶积电路的时间常数应与前级极零相消后指数函数的时间常数一致,电路中电阻R8的作用是防止电容C3的容抗太小导致导通电流过大,损坏后级运算放大器。电路中应确保R8 * C3的值远小于R7 * C3的值,确保反褶积电路的时间常数不受电阻R8影响。被反卷积还原的信号再通过一个高速比较器,输出的快通道脉冲信号即可被FPGA识别,从而开启一次测量流程。

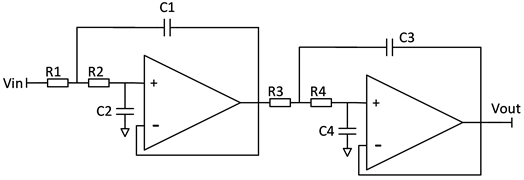

3.3. 滤波电路

前置放大器输出的放大信号除了核信号以外往往还有混杂噪声和其他干扰,为了提高系统精度需要对信号进行滤波以提高信噪比 [10]。

经过讨论与调试,本系统采用拥有最佳平坦度的巴特沃斯滤波器作为模型,采用sallen-key有源滤波器作为拓扑结构。巴特沃斯滤波器的特点是通频带内的频率响应曲线最大限度平坦,没有起伏,而在阻频带则逐渐下降为零。在振幅的对数对角频率的波特图上,从某一边界角频率开始,振幅随着角频率的增加而逐步减少,趋向负无穷大。sallen-key有源滤波器配置简单,输入阻抗高。其基本结构如下图7:

图7. sallen-key有源滤波器

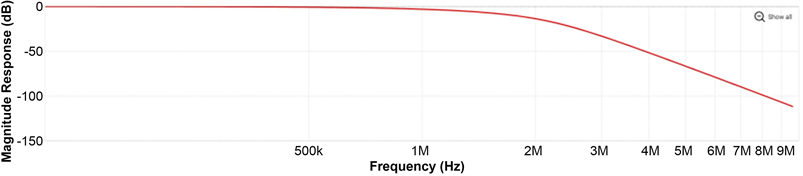

使用TI (德州仪器)的仿真软件Filter仿真1 Mhz的巴特沃斯低通滤波器,通过仿真获得频率响应图如下图8所示:

图8. 频率响应图

可以看出滤波器频响非常平坦,低通带宽点设置在1 Mhz处,适配峰值保持电路工作带宽范围。

4. 软件部分

本系统软件部分主要分为控制逻辑部分以及幅值分析部分,控制逻辑部分状态图如图9所示:

图9. 控制逻辑状态图

系统上电复位之后,控制逻辑部分状态机进入闲置状态,等待快通道触发,快通道脉冲之后将同时触发修正系统以及状态机进入寻峰状态。修正系统的功能是为了统计在高计数率下可能因为堆积而被系统判弃的核信号,进入寻峰状态之后,系统等待慢通道峰值保持成功的触发信号,若峰值保持电路工作正常,则会在有限时间内输出一个脉冲信号提醒FPGA进入采集状态,若是电路工作异常未产生峰值保持成功脉冲,则在一定超时状态之后会重新返回闲置状态。峰值点触发成功之后则进入到采集状态,FPGA驱动ADC进行模数转换,采集完成之后将进入到泄放状态,此状态将控制峰值保持电路泄放保持电容上的电荷,使电路处于闲置状态。并且将采集完成的ADC值发送到幅值计数系统。

为了适应不用场合下需要不同道址的场合,在程序中加入了道址切换功能,可以通过上位机发送命令切换道址,从256道址、512道址一直倍增到最高可支持16384道址。支持RS232、USB、以太网等通信方式传输数据。

5. PCB布局以及实物

除了原理设计以及器件选型上适配此系统的需求,规范的PCB布局也是保证信号完整的关键,需要严格遵守PCB设计规范,例如发热器件需要远离热敏元件、避免过近的平行走线、使用大铺地保证足够低的电流回路阻抗等。最终布局焊接好的PCB如图10所示:

图10. PCB实物图

6. 测试数据

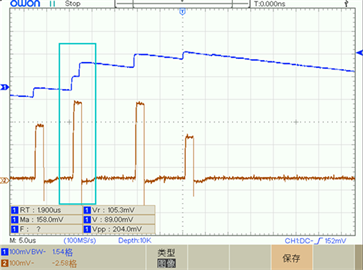

将北京跃成光子科技有限公司溴化澜探头探测137Cs辐射源的输出经过前置放大器放大之后的输出信号输入到此系统中,取前置放大器信号(通道1)和峰值保持信号(通道2)。可以看出前置放大器输出的信号时间常数较长,已经形成堆积,若是直接对此信号进行采样,谱线波形必然受到影响,而通过本系统输出的峰值保持波形还原并保持了正确的原始信号。同时在蓝色区域部分可以看出原始信号出现了两个非常接近的信号,但是峰值保持电路自动甄别并丢弃了后一个信号,提高谱线分辨率。数字电路部分也会自动将丢失的脉冲数量修正到总的计数率里面。测试结果如图11所示:

图11. 测试结果

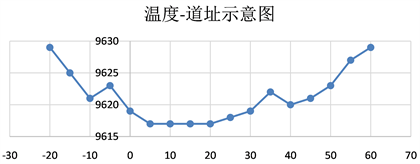

将多道置于恒温实验箱中,恒温箱设置50%湿度,改变温度测试本系统温度稳定性,测试数据如下(图12):

图12. 温度稳定性测试

通过观察,道址最大温度漂移发生在−20℃到−10℃这一段,经计算后漂移量为83.11 ppm/℃。此指标已经优于国外部分传统多道生产厂家。

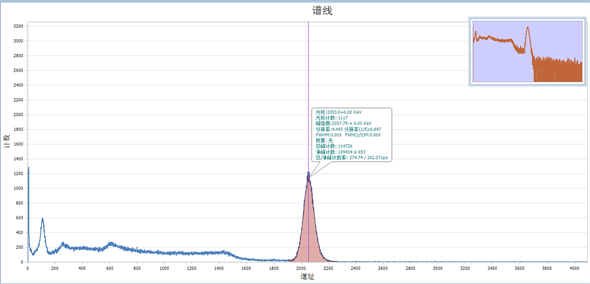

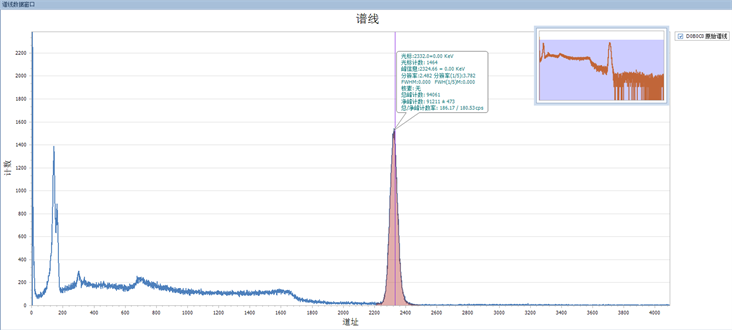

分辨率测试1:使用北京玻璃研究所CeBr3探头探测137Cs辐射源,将输出信号输入到本系统,最终测试分辨率为4.5%@662 keV,4096道址下成谱如下(图13):

图13. 分辨率测试1结果

分辨率测试2:使用北京跃成光子科技有限公司溴化澜探头探测137Cs,将输出信号输入到本系统,最终测试分辨率为2.5%@662 keV,8192道址下成谱如下(图14):

图14. 分辨率测试2结果

7. 总结与展望

本系统测试的谱线结果与其他同类仪器相比,能量分辨率较好,且所有元器件均为中国大陆内厂家自行研发生产,可以实现自给自足,填补了国内在本领域对国产化设计的空白。本系统依然存在部分不足,部分参数例如增益控制、触发阈值调节还未实现远程数字控制,信号链路不能方便地通过上位机查看,需要使用示波器协助观测。后面将继续针对以上存在的问题进行相应的研究,提高此系统的实用性。

高精度低温漂模数混合多道

摘要:核学科领域内经常要对辐射信号进行能谱测量,常见的多道测量系统分为模拟多道测量系统和数字多道测量系统。纯模拟多道系统会受到模拟器件限制导致其带宽较低、统计死区时间长、弹道亏损较为严重以及计数率低等缺点。而数字多道虽然对这些缺点有很大的改善,但是其成本较高、功耗大难以在低功耗以及民用领域得到推广。综合两者的优点,本文将模拟多道和数字多道融合在一起,改进一种新型的模数混合多道,让其继承各自的优点,提高分辨率和计数率的情况下减少成本以及系统功耗。最终使用低成本器件设计成功的模数混合多道搭配CeBr3和LaBr3闪烁体光电倍增管探头。测试137Cs源,在662 keV处分辨率为分别为4.5%@662 keV和2.5%@662 keV,达到了设计要求,有力地降低了成本并提升了性能。

关键词:多道,高分辨率,低温漂,低功耗