Design of Ultra-Low Power PMOS and NMOS for Nano Scale VLSI Circuits ()

1. Introduction

The need for low power chips is the increased marked demand for portable consumer electronics powered by the batteries, which have not experienced the similar rapid density growth compared to electronics circuits. It has been concluded that battery technology alone will not solve power problems in the near future. Therefore designing a chip with low power is becoming a major concern in the chip design industry. The different power reduction techniques from device level to circuit level and system level have been shown as a low power taxonomy [1] .

In ultra-deep submicron technology especially below 45 nm technology, leakage power is becoming a major concern than the dynamic power. As the technology is going on scaling down, and we are now in 20 nm/15 nm/ 10 nm technology proper controlling of leakage power is becoming challenge factor.

Any power reduction techniques at device level will certainly lower the overall power consumption at system level (power reduction means it should be applicable from device level to system level, there is no guarantee that device level power reduction always applicable at system level) [2] .

Related work: The existing numerous power reduction techniques in the field of VLSI are suitable for only 90 nm and above, but continuous scaling of the device in the present VLSI technology many of them may not be suitable. Moreover if the technique is suitable for power reduction than it fails for high speed, hence a new technique is required that is suitable for both power and speed [3] .

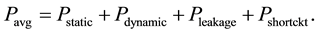

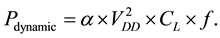

Sources of power dissipations are

The major source in the overall power dissipation is the dynamic power

α = transition activity factor, VDD = supply voltage, CL = load capacitance, f = frequency of operation.

As the technology shrinks leakage power is to be dealt very carefully.

2. Taxonomy of Low Power

In Figure 1 different power dissipation and power reduction techniques are clearly shown, all these techniques are applicable in low power design [4] .

3. Problem Statement

Here an attempt has been made to control leakage power by proposed PMOS and NMOS, the fundamental limit of conventional PMOS and NMOS is higher leakage and lower sped in deep submicron technology sine power

supply reduction lowers three times the threshold voltage will degrade the speed of the circuit considerably, as we are striving forward to higher level of integration, area is not having that much of concern, now we are in position to keep millions of transistors in a single die, the other performance parameters like power, speed and delay moreover power delay product are important parameters which can decide the role of the device in nano scale regime [5] . In design abstraction we are approaching bottom up design as shown in the below Figure 2, basically CMOS device level analysis is done and comparative study is done among different MOS devices.

Demerits of Conventional PMOS & NMOS

Figure 3(a) and Figure 3(b) show the conventional PMOS and NMOS and having the following demerits.

・ Lower speed.

・ Higher leakage in deep submicron technology.

Figure 4 in DT PMOS and DT NMOS body is connected to gate terminal of the MOS device and as the gate voltage is changing body biasing takes place.

Working of proposed PMOS and NMOS: in Figure 5 for top transistor (PM0) a reference voltage of 0.8 V is applied, and input is applied to the gate terminals of bottom transistor (PM2) and output is taken across the drain terminals of the right transistor (PM1) [6] .

Both the conventional PMOS and NMOS, DT PMOS, DT NMOS and proposed PMOS and proposed NMOS are implemented using 45 nm technology and all are simulated using Cadence Virtuoso Design Environment and simulated and results are shown Table 1. From Table 1 the proposed PMOS and NMOS have low PDP value.

Comparison table for the conventional PMOS and NMOS, DT PMOS, DT NMOS and proposed PMOS and proposed NMOS are implemented using 90 nm technology and all are simulated using Cadence Virtuoso Design Environment and simulated and results are shown Table 2.

Comparison table for the conventional PMOS and NMOS, DT PMOS, DT NMOS and proposed PMOS and proposed NMOS are implemented using 180 nm technology and all are simulated using Cadence Virtuoso Design Environment and simulated and results are shown Table 3.

![]() (a) (b)

(a) (b)

Figure 3. Conventional PMOS (a) & NMOS (b).

The PMOS and NMOS are good transfer of 1 and good transfer of 0, the comparative study is done on various types of MOS devices like PMOS, DTMOS and proposed MOS devices, the average power, delay and PDP is calculated by using the cadence virtuoso design environment tool for 45 nm, 90 nm, 180 nm technology [7] .

4. Conventional CMOS Inverter

Figure 6 shows a conventional CMOS inverter which is simulated using Cadence Virtuoso Design tool and simulated outputs are shown in Figure 7, Figure 8 shows CMOS output when all Zero’s Applied and Figure 9 shows CMOS output when All one’s Applied.

5. Inverter with Proposed PMOS and NMOS

From the Figure 10 for T6 and T3 applied a reference voltage of 0.8 V when Vin = 0 V applied T4 and T5 become on and output node will be 1 and T1, T2 will become off. When input is 1 T4, T5 will be non conducting and T2, T1 will become conducting will be zero as current sinks towards 0 v [8] . And output results are shown in the Figures 11-13.

![]()

Figure 7. Conventional CMOS inverter output.

![]()

Figure 8. CMOS output when all zero’s applied.

![]()

Figure 9. CMOS output when all one’s applied.

There may be an area overhead but this circuit is certainly suitable for high speed and low leakage in deep submicron technology, as area is not a problem since we are in a position to keep millions of transistors in single die, performance parameters like speed will increase and leakage will decrease [9] .

Hence an attempt has been made with proposed MOS devices to improve the performances.

![]()

Figure 12. Proposed CMOS output for all zero’s.

![]()

Figure 13. Proposed CMOS output for all one’s.

6. Leakage Current Mechanism

Reverse biased junction leakage and subthreshold leakage have very much similar characteristics both will be in order of pico amperes per device and very sensitive to process variations. Leakage current cannot be ignored in deep submicron region and leakage current is the beyond the digital designer control [10] . In large scale high performance digital chips performing operations with high frequency. In ultra submicron region leakage power is playing a major contribution apart of dynamic power [11] .

Subthreshold channel leakage: the subthreshold conduction current is given by ![]() where alpha is parameter depends on fabrication process vth is the threshold voltage, vth is the thermal voltage, even though a transistor is logically turned off there may be non zero leakage current through the channel this current is known as Subthreshold leakage current Since it occurs below threshold voltage [12] .

where alpha is parameter depends on fabrication process vth is the threshold voltage, vth is the thermal voltage, even though a transistor is logically turned off there may be non zero leakage current through the channel this current is known as Subthreshold leakage current Since it occurs below threshold voltage [12] .

7. Calculation of Leakage Power in CMOS Inverter and Proposed CMOS Inverter at 45 nm Technology

7.1. Normal CMOS Inverter Leakage Power

・ Power: 6.937 ´ 10‒9, delay: 0.05 ´ 10‒9.

・ When all ones applied power is 4.917 ´ 10‒12.

・ When all zeros applied power is 5.018 ´ 10‒12.

・ Total power for all ones and all zeros is 4.97 ´ 10‒12 + 5.018 ´ 10‒12 = 9.935 ´ 10‒12.

・ Leakage power = 6.937 ´ 10‒9 ‒ 9.935 ´ 10‒12 = 6927 ´ 10‒12.

7.2. Novel CMOS Inverter Leakage Power

・ AVG power P = 6.849 ´ 10‒9, delay = 0.18 ns.

・ Power when all ones applied = 6.655 ´ 10‒12.

・ Power when all zeros applied = 11.44 ´ 10‒12.

・ All ones + all zeros power = 6.655 ´ 10‒12 + 11.44 ´ 10‒12 = 1.8095 ´ 10‒11.

・ Leakage power = 6.849 ´ 10‒9 ‒ 1.8095 ´ 10‒11 = 6830 ´ 10‒12 w.

The difference of leakage between conventional CMOS and Proposed CMOS power is

6927 ´ 10‒12 ‒ 6830 ´ 10‒12 = 97 ´ 10‒12.

8. Conclusion

We designed a Novel PMOS and NMOS which could give superior performance in deep submicron technology. The MOS devices like PMOS, DTMOS, and Novel MOS are studied and PDP is comparatively calculated. The leakage power is calculated for normal CMOS inverter and Novel CMOS inverter and it is observed that Novel CMOS inverter has less leakage power compared to Normal CMOS inverter. There may be area overhead but performance is better. It is concluded that Novel PMOS and NMOS are certainly suitable for low leakage and low power in ultra-deep submicron technology [13] .