Circuits and Systems

Vol.06 No.05(2015), Article ID:56533,6 pages

10.4236/cs.2015.65014

A Subthreshold Low-Voltage Low-Phase-Noise CMOS LC-VCO with Resistive Biasing

Jungnam Bae1, Saichandrateja Radhapuram1, Ikkyun Jo1, Takao Kihara2, Toshimasa Matsuoka1

1Graduate School of Engineering, Osaka University, Osaka, Japan

2Faculty of Engineering, Osaka Institute of Technology, Osaka, Japan

Email: bae@si.eei.eng.osaka-u.ac.jp, teja@si.eei.eng.osaka-u.ac.jp, jo@si.eei.eng.osaka-u.ac.jp, takao.kihara@oit.ac.jp, matsuoka@eei.eng.osaka-u.ac.jp

Copyright © 2015 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received 4 March 2015; accepted 19 May 2015; published 22 May 2015

ABSTRACT

This paper presents a low-phase-noise LC voltage-controlled oscillator (LC-VCO) with top resistive biasing in subthreshold region. The subthreshold LC-VCO has low-power and low-phase-noise due to its high transconductance efficiency and low gate bias condition. The top resistive biasing has more benefit with the feature of phase noise than MOS current source since it can support the low-noise characteristics and large output swing. The LC-VCO designed in 130-nm CMOS process with 0.7-V supply voltage achieves phase noise of −116 dBc/Hz at 200 kHz offset with tuning range of 398 MHz to 408 MHz covering medical implant communication service (MICS) band.

Keywords:

VCO, Resistive Biasing, Current Source, CMOS Integrated Circuit, Phase Noise, MICS Band

1. Introduction

Integrated LC oscillators are important building blocks in the implementation of radio frequency (RF) front-end modules to provide a stable local oscillator (LO) signal for modulation/demodulation or up/down frequency conversion. RF transceivers for implanted medical device require miniaturized forms with low-power consumption and fully integration. The medical implant communication service (MICS) band in the frequency range of 402 MHz to 405 MHz is widely used for medical RF transceivers because the MICS band signals have reasonable propagation characteristics in human body and are well suited for achieving a good trade-off between size and power. Furthermore, the use of MICS band does not pose a significant risk of interference to other frequencies within or close to this band. The phase noise requirement for an oscillator operating in MICS band is less than −100 dBc/Hz at 200 kHz offset frequency [1] .

One of the major challenges in the design of RF front-end modules is implementation of fully integrated low- power, low-phase-noise voltage-controlled oscillators (VCOs). The CMOS devices operating in subthreshold region have an advantage of higher transconductance to power dissipation ratio with decent noise performance in comparison with the strong inversion region. Therefore, the subthreshold VCO achieves low-power and low-phase-noise characteristics. The circuits designed with MOS transistors biased in the subthreshold region operate with lowered voltage headroom, resulting in lower supply voltage. However, the phase noise performance is degraded due to the small amplitude at low supply voltages and it is recognized that the active current source for biasing purpose introduces noise performance degradation [2] [3] . There have been many efforts to improve the phase noise performance by improving the quality (Q) factor of the resonator or reducing the noise power [4] [5] . In this work, we focus on the current biasing technique in subthreshold region for better performance. The subthreshold-biased LC-VCO and resistive biasing technique are employed to achieve low-voltage operation and low phase noise.

This paper presents the analysis of phase noise performance through various biasing techniques, and a low- phase-noise LC-VCO is designed using resistive biasing instead of active current source scheme. The top resistive biasing is employed for low-phase-noise and low-voltage operation because of its inherent advantage of low effective noise and large voltage swing. This circuit has been designed in 130-nm CMOS technology with 0.7-V supply voltage. This paper is organized as follows. Section 2 presents the phase noise analysis in accordance with various biasing techniques. Section 3 describes the circuit design, and presents the simulation results. Finally, conclusions are drawn in Section 4.

2. Phase Noise Analysis of Biasing Techniques

There are many ways to realize the integrated LC-VCOs. For the analysis of the current biasing techniques, an NMOS cross-coupled differential pair is used for the core oscillator design, which has an advantage of common-mode noise suppression and low-voltage operation. The different cases of current biasing techniques in differential LC-VCO are shown in Figure 1. In general, the active biasing with MOS current sources,  and

and , (Figure 1(a) and Figure 1(b)) and passive biasing with resistors,

, (Figure 1(a) and Figure 1(b)) and passive biasing with resistors,  and

and , (Figure 1(c) and Figure 1(d)) are used to supply the bias current.

, (Figure 1(c) and Figure 1(d)) are used to supply the bias current.

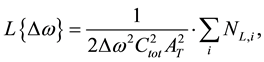

The phase noise in harmonic oscillators based on the linear time-variant (LTV) analysis approach is expressed as [6] [7]

(1)

(1)

where  is the offset angular frequency,

is the offset angular frequency,  is the total capacitance of LC resonator, AT is the oscillation amplitude across the LC resonator, and the effective noise power

is the total capacitance of LC resonator, AT is the oscillation amplitude across the LC resonator, and the effective noise power  is given by [7]

is given by [7]

(2)

(2)

where Tp is the oscillation time period,  is the noise current power spectral density per unit frequency

is the noise current power spectral density per unit frequency

generated by the i-th device, and  is the impulse sensitivity function (ISF) representing the time-varying sensitivity of the oscillator phase to perturbations. ISF is a dimensionless, amplitude-independent periodic function which describes how much phase shift occurs from applying a unit impulse at any point of time. The phase noise depends on the reciprocal of the oscillation amplitude. Based on the simple analytical model similar to [8] , the oscillation amplitude AT is given by

is the impulse sensitivity function (ISF) representing the time-varying sensitivity of the oscillator phase to perturbations. ISF is a dimensionless, amplitude-independent periodic function which describes how much phase shift occurs from applying a unit impulse at any point of time. The phase noise depends on the reciprocal of the oscillation amplitude. Based on the simple analytical model similar to [8] , the oscillation amplitude AT is given by

(3)

(3)

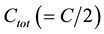

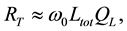

where  is the bias current and RT is the equivalent parallel resistance of the LC resonator. Among the components of LC resonator, Q factor of inductor is more dominant than of capacitor because inductor has lower Q factor than that of capacitor. So, RT can be calculated as

is the bias current and RT is the equivalent parallel resistance of the LC resonator. Among the components of LC resonator, Q factor of inductor is more dominant than of capacitor because inductor has lower Q factor than that of capacitor. So, RT can be calculated as

Figure 1. Current biasing techniques of (a) PMOS current source, (b) NMOS current source, (c) top resistive biasing, and (d) bottom resistive biasing.

(4)

(4)

where  is the oscillation angular frequency,

is the oscillation angular frequency,

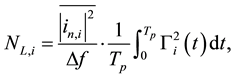

2.1. Effective Noise

Lower effective noise improves phase noise performance, and it depends on the noise source. The total effective noise of LC-VCO using MOS current source (Figure 1(a) and Figure 1(b)),

where

To reduce the noise from the MOS current source, a low-value resistor is employed as a practical biasing technique for LC-VCOs. In the case of using a resistor as current source, the thermal noise caused by MOS current source can be replaced by the thermal noise of the bias feeding resistor. Here, considering the differential- pair MOS switching action in resistive biasing case, the total effective noise for LC-VCO using resistive biasing (Figure 1(c) and Figure 1(d)),

where

asing position (top and bottom), and

Figure 2(a) represents the effective noise contribution for different biasing techniques. Typically, an NMOS transistor has a larger drain noise current than a PMOS transistor under the same drain current. So, the choice of using PMOS transistors as current source reduces the effective noise. However, PMOS current source case still has a large effective noise. Contrarily, resistive biasing techniques show low effective noise as they avoid the use of noisy MOS current source. Thermal noise from the bias feeding resistor as current source is low, and thereby it has small influence on phase noise.

2.2. Oscillation Amplitude

From the discussion in the above section, increasing oscillation amplitude reduces the phase noise. In Equation (3), the oscillation amplitude in LC-VCO is proportional to the equivalent parallel resistance of the LC resonator RT and bias current

Figure 2(b) shows I-V characteristic of the differential-pair part of the LC-VCO, which realizes small-signal negative resistance. In the bottom resistive biasing, this part is equivalent to a couple of common-source MOS devices with source degeneration resistor. The instantaneous gate-source voltage of the common-source MOS devices for bottom and top resistive biasing techniques (

where

gion is proportional to the exponential of the gate-source voltage. The gate-source voltage in bottom biasing is attenuated by the voltage drop across the bottom resistor. The subthreshold drain currents for two resistive biasing have the following relationship

Figure 2. (a) Effective noise contribution in NMOS and PMOS current sources (“NMOS CS” and “PMOS CS”) and top and bottom resistive (“RES Top” and “RES Bottom”) biasing techniques, (b) I-V characteristics of the differential-pair part, (c) oscillation amplitude, and (d) phase noise comparison (simulation results, 130-nm CMOS process, VDD = 0.7 V).

where

2.3. Comparison

Figure 2(d) shows the phase noise comparison for different biasing techniques. The phase noise results are obtained from the periodic steady-state circuit simulation with various current conditions. The resistive biasing techniques, which do not use noisy MOS current source, have 60% less effective noise than NMOS current source case. The low thermal noise introduced by a biasing resistance lower than nearly 1 kW does not influence the oscillator spectral purity. In aspect of biasing position, the bottom biasing technique degrades the oscillation amplitude due to the degradation of drain current. As a result, top resistive biasing technique has higher oscillation amplitude of 1.15 to 1.35 times than other biasing techniques. Taken together, the top resistive biasing technique has better phase noise performance because of smaller effective noise and large output swing.

3. Circuit Design and Simulation Results

In this study, the top resistive biasing is applied to design the LC-VCO operating at a 0.7-V supply for the MICS band. The structure of NMOS cross-coupled differential LC-VCO with top resistive biasing is shown in Figure 3(a). The MOS transistors optimally biased in subthreshold region

4. Conclusion

A low-voltage low-phase-noise LC-VCO operating in subthreshold region using top resistive biasing is presented. The subthreshold-biased LC-VCO achieves low-power consumption, and the lower gate bias provides the phase noise improvement. The LC-VCO using top resistive biasing operates from 398 MHz to 408 MHz and exhibits a phase noise of −116 dBc/Hz at 200 kHz offset frequency with an improvement of 1 dB to 6 dB compared with other biasing techniques in similar conditions. Designed LC-VCO consumes 700 μW from a 0.7-V

Figure 3. (a) Schematic of LC-VCO with top resistive biasing, (b) phase noise and current consumption in accordance with top resistance, (c) phase noise performance, and (d) tuning range.

supply. In comparison of the biasing techniques, the top resistive biasing has least effective noise power because of the elimination of noisy MOS current source, and has a large output swing because of no current degradation. Therefore, the top resistive biased LC-VCO realizes the low-voltage operation with better phase noise performance.

Acknowledgements

The IC in this study is designed as part of the chip fabrication program of the VDEC at the University of Tokyo in collaboration with Cadence Design Systems.

References

- Bradley, P.D. (2006) An Ultra Low Power, High Performance Medical Implant Communication System (MICS) Transceiver for Implantable Devices. IEEE Biomedical Circuits and Systems Conference, London, 29 November-1 December 2006, 158-161.

- Hajimiri, A. and Lee, T.H. (1999) Design Issues in CMOS Differential LC Oscillators. IEEE Journal of Solid-State Circuits, 34, 717-724.

- Soltanian, B. and Kinget, P.R. (2006) Tail Current-Shaping to Improve Phase Noise in LC Voltage-Controlled Oscillators. IEEE Journal of Solid-State Circuits, 41, 1792-1802.

- Svelto, F., Deantoni, S. and Castello, R. (2000) A 1.3 GHz Low-Phase Noise Fully Tunable CMOS LC VCO. IEEE Journal of Solid-State Circuits, 35, 356-361.

- De Astis, G., Cordeau, D., Paillot, J.-M. and Dascalescu, L. (2005) A 5-GHz Fully Integrated Full PMOS Low- Phase-Noise LC VCO. IEEE Journal of Solid-State Circuits, 40, 2087-2091.

- Lee, T.H. and Hajimiri, A. (2000) Oscillator Phase Noise: A Tutorial. IEEE Journal of Solid-State Circuits, 35, 326- 336.

- Mazzanti, A. and Andreani, P. (2008) Class-C Harmonic CMOS VCOs, with a General Result on Phase Noise. IEEE Journal of Solid-State Circuits, 43, 2716-2729.

- Yamashita, F., Matsuoka, T., Kihara, T., Takobe, I., Park, H.-J. and Taniguchi, K. (2009) Analytical Design of a 0.5V 5GHz CMOS LC-VCO. IEICE Electronics Express, 6, 1025-1031.

- Andreani, P., Wang, X., Vandi, L. and Fard, A. (2005) A Study of Phase Noise in Colpitts and LC-Tank CMOS Oscillators. IEEE Journal of Solid-State Circuits, 40, 1107-1118.

- Hegazi, E., Sjoland, H. and Abidi, A.A. (2001) A Filtering Technique to Lower LC Oscillator Phase Noise. IEEE Journal of Solid-State Circuits, 36, 1921-1930.

- Andreani, P. and Sjoland, H. (2002) Tail Current Noise Suppression in RF CMOS VCOs. IEEE Journal of Solid-State Circuits, 37, 342-348.

- Burghartz, J.N., Jenkins, K.A. and Soyuer, M. (1996) Multilevel-Spiral Inductors Using VLSI Interconnect Technology. IEEE Electron Device Letters, 17, 428-430.