# Design of Digital to Analog Converters with Arbitrary Radix

## **Tejmal S. Rathore**

Department of Electrical Engineering, IIT Goa, Farmagudi, India Email: tsrathore@iitgoa,ac.in

How to cite this paper: Rathore, T.S. (2018) Design of Digital to Analog Converters with Arbitrary Radix. *Circuits and Systems*, **9**, 49-57. https://doi.org/10.4236/cs.2018.93005

**Received:** January 6, 2018 **Accepted:** March 13, 2018 **Published:** March 16, 2018

Copyright © 2018 by author and Scientific Research Publishing Inc. This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Open Access

## Abstract

There are DAC structures available in the literature for radix r = 2, 3, and 4; but how they are arrived at is missing. No general structure is available for any radix r. The aim of the paper is, therefore, to fulfil these gaps. To start with, the design relations are derived for the simplest possible attenuator circuit when connected to a voltage source V and a series resistance R, such that the complete circuit offers the Thevenin resistance R. Spread relations for this attenuator are derived. An example when 3 such attenuators with different attenuation constants are connected in cascade is given. Interestingly, the two attenuators with attenuator is then obtained when *N* number of identical attenuators are connected in cascade. This is modified to derive a digital to analog converter for any radix r.

# **Keywords**

Digital to Analog Converter, Design of DAC, DAC of any Radix, DAC Structure

# **1. Introduction**

Multiple logics have several advantages over binary ones. Therefore, many multiple logic circuits have been developed [1]-[7]. Due to all these applications, there has been an interest in digital to analog converters (DACs) since long [8]-[16]. Binary to analog conversion (B/A) (radix 2) is very popular. Miyata *et al.* [8] and Current [9] deal with ternary (T/A) and quaternary (Q/A) (radices 3 and 4, respectively), to analog conversion. But none of these gives how the structures are arrived at. In [9] quaternary to analog conversion is obtained directly from that of radix 2 and compared with that R, 4/3R, 3R ladder DAC. It is shown that the Q/A requires 26% less total resistance if fabricated and approximately 15% more if assembled with discrete resistors of one value by series and parallel combinations of resistors. No generalized design is available for DACs with arbitrary radix r.

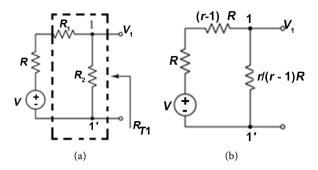

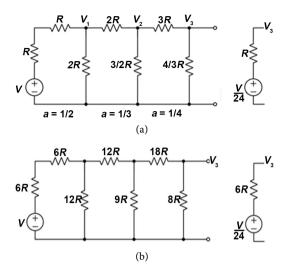

This paper gives the design of ladder DACs for any radix r. B/A, T/A, Q/A converters are the special cases. Conditions will be derived when N number of attenuators (one such attenuator is shown in **Figure 1(a)** in dashed line box) are cascaded so that the Thevenin voltage will be aV, a = 1/r is the attenuation factor (AF), while the Thevenin resistance is R. Such a structure is further modified for realizing ladder DACs for any radix r = 1/a.

## 2. Design of Ladder DACs

### 2.1. Basic Attenuator

Consider the circuit shown in **Figure 1(a)** where the simplest possible attenuator (potential divider) shown in dashed line box. Its Thevenin voltage

$$V_1 = \frac{R_2}{R_2 + R_1 + R} V = aV$$

(1)

where

$$a = \frac{R_2}{R_2 + R_1 + R}$$

(2)

is the AF. Thevenin resistance  $R_{T1}$  as seen from 1-1' in Figure 1(a) can be made equal to R, first increasing R by a series resistance  $R_1$  and then restoring it by connecting a parallel resistance  $R_2$ . Thus the condition is

$$R_{T1} = \frac{R_2(R_1 + R)}{R_2 + R_1 + R} = R.$$

(3)

Solving for  $R_1$ , we get

$$R_1 = \left(\frac{1-a}{a}\right)R = (r-1)R.$$

(4)

From (2) and (4), we get

$$R_2 = \left(\frac{1}{1-a}\right)R = \left(\frac{r}{r-1}\right)R.$$

(5)

After substituting the values of  $R_1$  and  $R_2$  in circuit of **Figure 1(a)**, we get the circuit shown in **Figure 1(b)**. To avoid the fractional value of  $R_2$ , we scale up all the resistance values by a factor (r - 1). Scaled circuit is shown in **Figure 2(a)**.

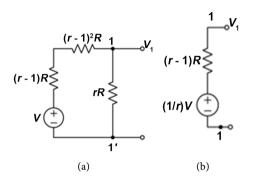

Note that, if a voltage V is applied in series with rR instead of (r-1)R, as shown in Figure 2(a), Thevenin voltage will be [(r-1)/r]V with the same Thevenin resistance  $R_{T1}$ .

#### 2.2. Spread

Out of the three resistance values (r-1), r and  $(r-1)^2$  in **Figure 2** the minimum value is r-1, and the maximum value is  $(r-1)^2$  as long as  $(r-1)^2 \ge r$ , *i.e.*, when  $r \ge 2.6$  and  $\le 0.36$ . For integer values of r,  $r \ge 3$  as r cannot be negative.

**Figure 1.** (a) A simplest possible attenuator; (b) Attenuator with values.

**Figure 2.** Scaled circuit of **Figure 1(b)** and its Thevenin equivalent.

Spread

$$S = \frac{R_{\max}}{R_{\min}} = \begin{cases} \frac{(r-1)^2}{r-1} = r-1, \ r \ge 3\\ \frac{r}{r-1}, \qquad r = 2 \end{cases}.$$

(6)

Note that the spread is 2 for both r = 2 and 3.

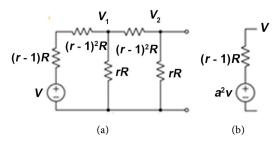

## 2.3. Cascaded Attenuator

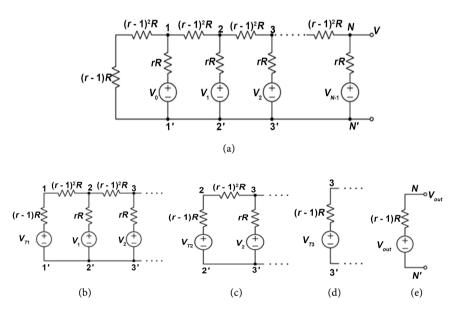

If one more section is cascaded as shown in **Figure 3(a)**, it can easily be seen that Thevenin voltage is

$$V_2 = \frac{R_2}{R_2 + R_1 + R} aV = a^2 V$$

(7)

and Thevenin resistance is still *R*. The Thevenin equivalent is shown in **Figure 3(b)**.

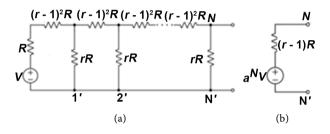

Thus if N number of sections are connected in cascade as shown in **Figure 4(a)**, then Thevenin voltage will be

$$V_n = a^N V \tag{8}$$

and the Thevenin resistance will be R. The equivalent circuit is shown in **Figure 4(b)**.

Figure 3. (a) Cascaded 2 sections, (b) Thevenin equivalent circuit.

Figure 4. (a) Cascaded *n*-sections, (b) Thevenin equivalent circuit.

As an application of the above theory, **Figure 5** shows a circuit which has 3 attenuators in cascade with r = 2, 3, 4.

It may be noted that the Thevenin voltage and the node voltage are the same as long as attenuator is not loaded. Hence in a chain of cascaded attenuator only the last one will have this property; all others do change their node voltages. This aspect is further discussed in section on practical results. Note that the spread, from Equation (6), is 2.25; while this would have been 23 if a single attenuator with a = 1/24 were used.

#### 2.4. DAC Circuit

Let us consider the circuit of **Figure 4** with voltage sources connected as shown in **Figure 6(a)**. After replacing the portion of the circuit left to 11' by Thevenin equivalent the circuit becomes as shown in **Figure 6(b)** where

$$V_{T1} = \frac{r-1}{r} V_o.$$

(9)

Repeating the similar step across the terminals 22' and using superposition theorem, the circuit reduces to that shown in Figure 6(c) where

$$V_{T2} = \frac{r-1}{r^2} V_o + \frac{r-1}{r} V_1 = \frac{r-1}{r^2} [V_o + rV_1].$$

(10)

Repeating the same across terminals 33', the circuit reduces to that shown in **Figure 6(d)**.

$$V_{T3} = \frac{r-1}{r^3} V_o + \frac{r-1}{r^2} V_1 + \frac{r-1}{r} V_2$$

$$= \frac{(r-1)}{r^3} \left[ V_o + r V_1 + r^2 V_2 \right].$$

(11)

**Figure 5.** (a) 3 cascaded sections with different AFs; (b) Circuit after scaling with a factor of 6.

**Figure 6.** (a) Ladder with voltage sources, (b)-(e) circuits after applying successively Thevenin theorem.

Proceeding in this manner, we can write for the entire circuit of Figure 4(a),

$$V_{out} = \frac{r-1}{r^N} \sum_{k=0}^{N-1} r^k V_k.$$

(12)

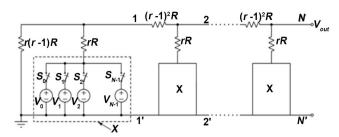

Now we modify the circuit as shown in **Figure 7** where switches  $S_k(k = 1, N - 1)$  are inserted which are operated by digital input. Depending upon the bit value, the particular switch connects to different weighted voltages according to the radix *r*. Thus the output voltage is proportional to the analog value of the digital input.

The resistance values in **Figure 7** are the same for r = 2 as given in [17] [18], for r = 3 given in [8] after scaling by a factor 2/3, and for r = 4 given in [9].

Figure 7. Digital to analog voltage converter.

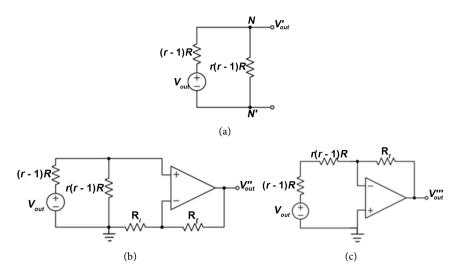

A resistance of value (r - 1) is connected across terminals NN' so as to make the ladder symmetrical. This is shown in **Figure 8(a)**. This will, however, reduce the voltage to

$$V_{out}' = \frac{r}{r+1} V_{out}.$$

(13)

This DAC, if connected to some circuit, will be further loaded. To avoid this loading, one can connect a non-inverting amplifier at the output as shown in **Figure 8(b)**. This will have an extra advantage of adjusting the gain to any desired value by choosing  $R_f$ . However, one resistance can be reduced, if an inverting amplifier is used, as shown in **Figure 8(c)**, wherein the resistance of r(r - 1) is connected to virtual ground instead of actual ground. Again the desired gain can be adjusted by choosing proper value for  $R_f$ . If a positive output is required, then the polarity of all the weighted reference voltages can be changed to negative.

## **3. Practical Results**

The circuits shown in **Figure 5(b)** and that in **Figure 7** for radix 3 and number of bits N = 3, were assembled. The resistances used were 10% tolerance, OA used is 741, resistances were connected in series and/or parallel to have the desired values. Voltage used for **Figure 5(b)** is 12 V and for **Figure 6** were +15 V, -15 V, 4.5 V and 9 V.

The calculated values of voltages  $V_1$ ,  $V_2$  and  $V_3$  are  $(4.54 \neq 6 \text{ V}, 1.625 \neq 2 \text{ V}, 0.5 \text{ V}$ , respectively, using node analysis, and the corresponding practically measured values are 4.6 V, 1.82 V and 0.5 V which are in close agreement.

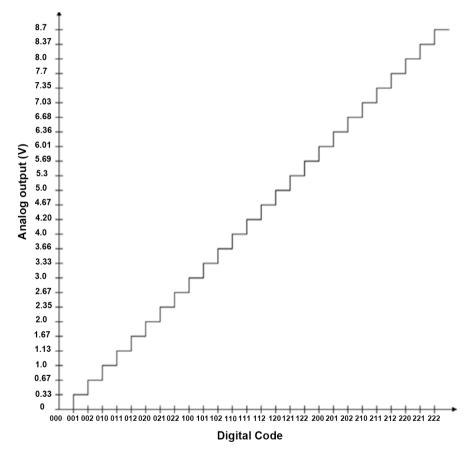

Following 3 sets of measurements were made for the DAC: 1) without any resistance  $r(r-1)R = 6 \text{ k}\Omega$  at the output, 2) with resistance 6 k $\Omega$  connected across NN' and 3) with inverting amplifier of gain -3/2. Resistance values chosen as  $R_1$ = 4 k $\Omega$ ,  $R_2$  = 3 k $\Omega$ , and R = 2 k $\Omega$ ,  $R_f$  = 8 k $\Omega$ . The analog voltage output  $V_{out}^{m}$ versus the digital input for set (3) are plotted in **Figure 9**. In all the cases, the practical results were in close agreement with the theoretically expected results. For example, when the digital input given is 200, the output  $V_{out}$  = 6.01 V (6 V),  $V_{out}'$  = 4.53 V (4.5 V) and  $V_{out}^{m}$  = 6.04 (6 V). The bracket values are the theoretically expected ones. These results show that the DAC exhibits the practical response very closely the expected theoretical one.

**Figure 8.** (a) Circuit with additional resistance connected; (b) Circuit with non-inverting amplifier; (c) Circuit with inverting amplifier.

Figure 9. Plot of analog voltage output versus digital input.

# 4. Conclusion

Design relations have been derived for the simplest possible attenuator circuit when connected to a voltage source of voltage V and a series resistance R, such that the complete circuit offers the Thevenin Resistance R. Spread relations for

the circuit have been derived. An example when 3 such attenuators with different attenuation constants are connected in cascade has been given. Interestingly, the two attenuators with attenuation factors 1/2 and 1/3 have the same spread of 2. A generalized attenuator has been obtained when N number of identical attenuators are connected in cascade. This has been used to derive a general digital to analog converter for any radix r. Specific circuits were assembled in the laboratory and practical results were taken. These results match closely with the expected theoretical ones.

## Acknowledgements

The author acknowledges with thanks the help rendered by Dr. Nandakumar in drawing nice figures, Mr. Siddharth Kala for taking the practical results. He wishes to thank the reviewer for the constructive suggestions.

## References

- [1] Stark, M. (1981) Two-Bits per Cell ROM. COPCON Dig. Papers, 209-212.

- [2] Dao, T.T. (1977) Threshold I<sup>2</sup>L and Its Application to Binary Symmetric Function and Multivalued Logic. *IEEE Journal of Solid-State Circuits*, **12**, 463-472. https://doi.org/10.1109/JSSC.1977.1050939

- Friedman, N., Salama, C. and Thompson, P. (1977) Realization of Multi-Valued I<sup>2</sup>L Full Adder. *IEEE Journal of Solid-State Circuits*, 12, 532-534.

- [4] Current, K.W. and Mow, D.A. (1978) Four-Valued Threshold Logic Full Adder Circuit Implementations. *Proceedings of the Eighth International Symposium on Multiple-Valued Logic*, Rosemont, 1 April 1978, 95-100.

- [5] Current, K.W. and Mow, D.A. (1979) Implementing Parallel Counters with Four-Valued Threshold Logic. *IEEE Transactions on Computers*, C-28, 200-204. <u>https://doi.org/10.1109/TC.1979.1675320</u>

- [6] Hallworth, R.P. and Heath, F.G. (1961) Semiconductor Circuits for Ternary Logic. *IEEE Monograph*, 109C, 219-225.

- [7] Porat, D.I. (1969) Three-Valued Digital Systems. Proceedings of the IEEE, 116, 947-954. https://doi.org/10.1049/piee.1969.0177

- [8] Miyata, T., Tamagawa, K. and Watahiki, T. (1979) Ternary-to-Analog Converters Using Resistor Ladders. *Proceedings of the IEEE*, 67, 1165-1166. https://doi.org/10.1109/PROC.1979.11414

- Current, K.W. (1982) Quaternary-to-Analog Conversion with Resistive Ladders. *Proceedings of the IEEE*, 70, 408-409. <u>https://doi.org/10.1109/PROC.1982.12319</u>

- [10] Faruque, S.M., Bhattacharyya, B.B. and Rathore, T.S. (1992) A Switched-Capacitor Based Digital-to-Analog Converter. *Journal of the Institution of Engineers*, 72, 115-116.

- Faulkner, E.A. (1983) Improved Method of Digital/Analog and Analog/Digital Conversion. *Electronics Letters*, 19, 896-897. <u>https://doi.org/10.1049/el:19830610</u>

- [12] Rathore, T.S. (1998) Optimized Weighted-Resistor Digital to Analog Converter. *IEE Proceedings-Circuits Devices and Systems*, 145, 197-200. https://doi.org/10.1049/ip-cds:19981814

- [13] Rathore, T.S. (1999) A Novel Ladder Digital to Analog Converter. *IETE Journal of Education*, 40, 21-22. <u>https://doi.org/10.1080/09747338.1999.11415691</u>

- [14] Rathore, T.S. and Jain, A. (1998) A New Economical 2R-3R-4R Ladder Digital to analog converter. *IETE Technical Review*, 15, 289-290. <u>https://doi.org/10.1080/02564602.1998.11416761</u>

- [15] Rathore, T.S. and Jain, A. (1998) Abundance of Ladder Digital to Analog Converters. *IEEE Transactions on Instrumentation and Measurement*, **IM-50**, 1445-1449.

- [16] Rathore, T.S. (2003) Digital Measurement Techniques. 2nd Edition, Alpha Scientific International Ltd., Pangbourne.

- [17] Millman, J. (1979) Microelectronics. McGraw-Hill Int Book Co., Japan.

- [18] Taub, H. and Schilling, D. (1977) Digital Integrated Electronics. Tata McGraw-Hill, New Delhi.