# Canonic Realizations of Voltage-Controlled Floating Inductors Using CFOAs and Analog Multipliers

## Raj Senani<sup>1\*</sup>, Data Ram Bhaskar<sup>2,3</sup>, Munish Prasad Tripathi<sup>4</sup>, Manoj Kumar Jain<sup>5</sup>

<sup>1</sup>Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology, New Delhi, India

<sup>2</sup>Department of Electronics and Communication Engineering, Faculty of Engineering and Technology, Jamia Millia Islamia, New Delhi, India

<sup>3</sup>Department of Electronics and Communication Engineering, National Institute of Technology, Ashok Rajpath, Bihar, India

<sup>4</sup>Department of Electronics Engineering, Institute of Engineering and Technology, Lucknow, India

<sup>5</sup>Department of Electronics Engineering, Institute of Engineering and Technology, Lucknow, India

Email: \*senani@ieee.org, drbset@yahoo.com, munishprasadtripathi@rediffmail.com, mkjain71@gmail.com

How to cite this paper: Senani, R., Bhaskar, D.R., Tripathi, M.P. and Jain, M.K. (2016) Canonic Realizations of Voltage-Controlled Floating Inductors Using CFOAs and Analog Multipliers. *Circuits and Systems*, **7**, 3617-3625.

http://dx.doi.org/10.4236/cs.2016.711306

**Received:** May 11, 2016 **Accepted:** May 26, 2016 **Published:** September 8, 2016

Copyright © 2016 by authors and Scientific Research Publishing Inc. This work is licensed under the Creative Commons Attribution International License (CC BY 4.0). http://creativecommons.org/licenses/by/4.0/

#### Abstract

New voltage-controlled floating inductors employing CFOAs and an analog multiplier have been presented which have the attractive features of using a canonic number of passive components (only two resistors and a capacitor) and not requiring any component-matching conditions and design constraints for the intended type of inductance realization. The workability and applications of the new circuits have been demonstrated by SPICE simulation and hardware experimental results based upon AD844-type CFOAs and AD633-type/MPY534 type analog multipliers.

#### **Keywords**

Voltage Controlled Inductors, Floating Inductors, Inductance Simulation, Current Feedback Op-Amps, Analog Multipliers, Analog Circuits

## **1. Introduction**

Voltage-controlled-resistors and a variety of other voltage-controlled impedances are useful elements in the realization of electronically-controllable filters and oscillators and have been investigated in past using a variety of active elements such as op-amps, operational transconductance amplifiers, operational mirrored amplifiers, current conveyors and current feedback op-amps, for instance, see [1]-[13] and the references cited therein.

A recent paper [14] published in this Journal has presented two configurations for realizing voltage-controlled floating inductance (VC-FI) realization using thee/four Current feedback op-amps (CFOA) along with an analog multiplier. The first circuit of [14] employs four CFOAs, three resistors, a grounded capacitor and an analog multiplier and has been shown<sup>1</sup> to realize lossless VC-FI providing inductance value proportional to an external control voltage  $V_{c}$ . On the other hand, the second circuit of [14] employs one multiplier and as many passive components as in the former circuit, but uses one less CFOA to realize a lossless VC-FI inversely proportional to  $V_c$ . The circuits proposed in [14] however, suffer from two drawbacks: (i) employment of non-canonic number of resistors (three) and (ii) requirement of certain conditions/constraints to realize the intended type of FIs.

The purpose of this article is to present four new circuits which, in contrast to the circuits of [14] quoted above, employ a *canonic* number of resistors (only two) and, unlike the quoted circuits of [14], do not require any component-matching/realization conditions.

### 2. Canonic Realizations of Lossless Voltage-Controlled **Floating Inductors**

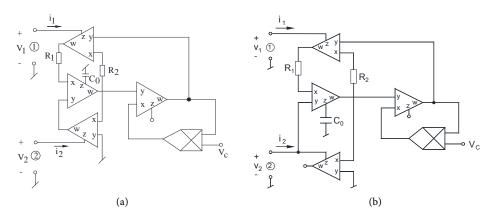

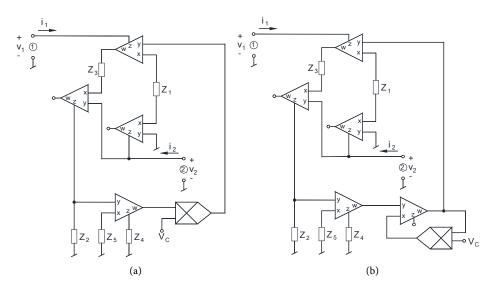

The proposed circuits, which employ canonic number of only two resistors and a grounded capacitor (GC) for realizing lossless VC-FIs, are shown in Figure 1 and Fig**ure 2** respectively. The proposed circuits are obtained by appropriate embedding<sup>2</sup> of an analog divider (as in the circuits of Figure 1) and analog multiplier (as in the circuits of Figure 2) into appropriate lossless floating inductance circuits [17] [18]. By a straight forward analysis, assuming the CFOAs to be characterized by  $i_y = 0$ ,  $v_x = v_y$ ,  $i_z = i_x$

Figure 1. Proposed circuits for realizing VC-FI proportional to VC.

<sup>1</sup>For the correction of some discrepancies in the analysis in the quoted circuits of [14] and an anomaly in the citation of an earlier work therein, see Appendix 1.

<sup>2</sup>The techniques of embedding analog dividers and analog multipliers (as in the circuits of Figure 1, Figure 2 and Figure 5 here which have their origin in the earlier works of [15]-[18]) to create op-amp-AM-based voltage-controlled-resistors have been taught by the first author (RS) in the course on Linear Integrated Circuits since 1990 and these unpublished ideas have been adopted by and circulated amongst the academic fraternity at numerous institutions freely.

Figure 2. Proposed circuits for realizing VC-FI inversely proportional to VC.

and  $v_w = v_z$ , both the circuits of **Figure 1** are found to be characterized by the following short-circuit admittance matrix:

$$\begin{bmatrix} i_1\\i_2 \end{bmatrix} = \left(\frac{V_{ref}}{V_c}\right) \left(\frac{1}{sC_0R_1R_2}\right) \begin{bmatrix} 1 & -1\\-1 & 1 \end{bmatrix} \begin{bmatrix} v_1\\v_2 \end{bmatrix}$$

(1)

Thus, the circuits realize an equivalent floating inductance  $L_{eq} = C_0 R_1 R_2 (V_c / V_{ref})$ . Note that, in contrast to the circuit of **Figure 2(a)** of [14] which requires matching of two resistors therein namely,  $R_2 = R_3$  to realize the intended type of VC-FI, the circuits of **Figure 1** here do not require any design constraints/conditions to be fulfilled to realize a VC-FI.

Consider now the circuits of **Figure 2**. By straight forward analysis, these two circuits are characterized by the following equation:

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \left(\frac{V_c}{V_{ref}}\right) \left(\frac{1}{sC_0R_1R_2}\right) \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

(2)

These circuits, therefore, realize an equivalent VC-FI of value  $L_{eq} = C_0 R_1 R_2 \left( V_{ref} / V_c \right)$ . In this case also, it must be pointed out that while the circuit of **Figure 3(a)** of [14] requires two conditions namely  $R_2 \gg R_1$  and  $(R_1 + R_2 = R_3)$ , no such conditions or constraints are needed in the new proposed circuits of **Figure 2**.

Lastly, it must also be noticed that in contrast to the circuits of Figure 2(a) and Figure 3(a) of [14] both of which require three resistors, the proposed new circuits require a bare minimum of only two resistors!

## 3. Applications of the Proposed VC-FIs, SPICE Simulation and Experimental Results

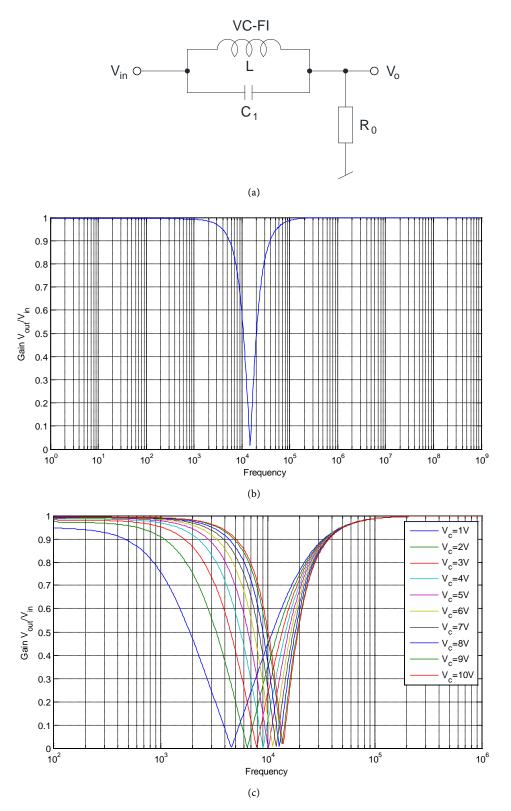

To check the workability of the proposed circuits, all the VC-FIs were tested by utilizing them in the realization of a second-order voltage-controllable notch filter as shown in **Figure 3(a)**. The frequency response of the notch filter employing the VC-FI of **Figure 1(a)** and designed to obtain a notch frequency of 15.9 kHz is shown in **Figure 3(b)**. **Figure 3(c)** shows the variability of the notch frequency with respect to the control voltage  $V_c$  for the notch filter when it was realized by using the VC-FI of **Figure 2(a)**.

**Figure 3.** SPICE simulation results: (a) A voltage-controllable notch filter; (b) Frequency response of the notch filter realized by using the VC-FI of **Figure 1(a)**; and (c) Variation of notch frequency with control voltage ( $V_c$ ) with the notch filter realized using the VC-FI of **Figure 2(a)**.

In the simulations, AD844 type CFOAs were used which were biased with  $\pm 12$  V DC power supplies. The simulation results of Figure 3(b) and Figure 3(c) are seen to be in close agreement with the theoretical results.

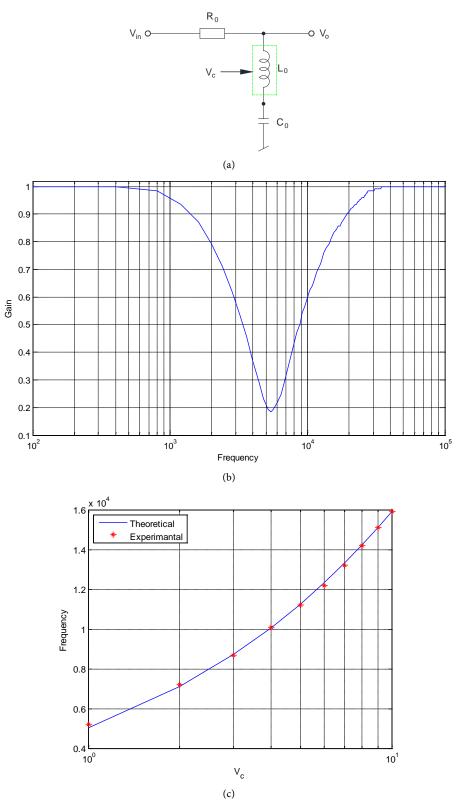

For verifying the practical validity of the proposed VC-FI formulations, we present here the results of the hardware implementation of a voltage-controlled band reject filter (shown in **Figure 4(a)**) wherein the VC-FI was implemented with the configuration of **Figure 2(b)**. AD844 type CFOAs biased with ±12 volts and MPY534 type analog multipliers biased with ±12 V were used along with the following component values:  $R_1$ = 1 k  $\Omega$ ,  $R_2$  = 1 k  $\Omega$ ,  $C_1$  = 1.0 nF,  $R_0$  = 680  $\Omega$  to obtain  $f_0$  = 5.2 kHz and bandwidth = 5.58 kHz.  $V_c$  was varied from 1 to 10 volts to vary the center frequency. An exemplary frequency response for  $V_c$  = 1 volt is shown in **Figure 4(b)** whereas the variability of  $f_0$ with respect to  $V_c$  has been shown in **Figure 4(c**).

The SPICE simulation results of **Figure 3** and the experimental results of **Figure 4**, thus, confirm the feasibility of the proposed formulations.

### 4. Concluding Remarks

Four new lossless VC-FIs are introduced which employ a canonical number of passive components (namely, only one GC and two resistors) and realize the intended type of floating inductances without any conditions/design constraints. This is in contrast to the recently reported circuits of [14] for the same purposes which suffer from the drawback of employing a non-canonical number of resistors (three) and requirement of component matching/design constraint to be fulfilled.

The workability of the new circuits as VC-FIs and the variability of the inductance value through an external control voltage  $V_c$  were demonstrated by SPICE simulation results of a notch filter, as well as through experimental results of another voltage-controlled notch filter.

It is expected that the proposed new circuits may find applications in situations requiring voltage-controlled inductors.

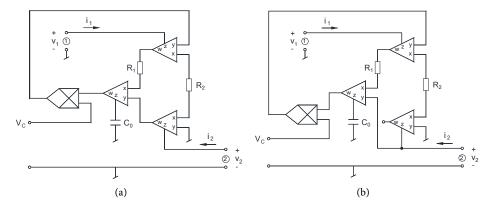

Lastly, it may be mentioned that the realization of many other grounded/floating, positive/negative and generalized linear voltage controlled impedances, based upon the ideas contained in [15]-[18] are possible; for instance, see the two configurations of **Figure 5** both of which realize VC-floating generalized impedance converters/inverters having equivalent floating impedance values given by:

$$Z_{1-2} = \left(\frac{V_{ref}}{V_c}\right) \frac{Z_1 Z_3 Z_5}{Z_2 Z_4}$$

(3)

and

$$Z_{1-2} = \left(\frac{V_c}{V_{ref}}\right) \frac{Z_1 Z_3 Z_5}{Z_2 Z_4} \tag{4}$$

respectively. The circuits of **Figure 1** and **Figure 2** can also be generalized similarly by replacing  $R_1$ ,  $R_2$  and  $C_0$  by impedances  $Z_1$ ,  $Z_2$  and  $Z_3$  respectively.

Figure 4. Experimental results of (a) the band reject filter using the VC-FI of Figure 2(b); (b) experimentaly measured frequency response; (c) variation of the centre frequency with the controlled voltage.

**Figure 5.** Two exemplary circuits realizing voltage-controlled floating generalized *impedance inverters/converters*.

Furthermore, the negative floating impedances are realizable from the configurations of **Figure 1**, **Figure 2** and **Figure 5**, by the simple artifice of interchanging some connections in the manner outlined earlier in [16] and [18], while various types of grounded positive/negative voltage controlled impedances are realizable by shorting port 2 to ground (thereby also leading to a reduced number of CFOAs in each case).

#### References

- Nay, K.W. and Budak, A. (1983) A Voltage-Controlled Resistance with Wide Dynamic Range and No Distortion. *IEEE Transactions on Circuits and Systems*, **30**, 770-772. <u>http://dx.doi.org/10.1109/TCS.1983.1085290</u>

- [2] Nay, K.W. and Budak, A. (1985) A Variable Negative Resistance. *IEEE Transactions on Circuits and Systems*, 32, 1193-1194. <u>http://dx.doi.org/10.1109/TCS.1985.1085637</u>

- [3] Senani, R. and Bhaskar, D.R. (1991) Realization of Voltage-Controlled Impedances. *IEEE Trans. Circuits and Systems*, 38, 1081-1086; 162. <u>http://dx.doi.org/10.1109/31.83879</u>

- [4] Senani, R. and Bhaskar, D.R. (1992) A simple Configuration for Realizing Voltage-Controlled Impedances. *IEEE Transactions on Circuits and Systems*, **39**, 52-59. <u>http://dx.doi.org/10.1109/81.109244</u>

- [5] Senani, R. and Bhaskar, D.R. (1994) Versatile Voltage-Controlled Impedance Configuration. *IEE Proceedings—Circuits, Devices and Systems*, 141, 414-416. <u>http://dx.doi.org/10.1049/ip-cds:19941296</u>

- Senani, R. (1995) Universal Linear Voltage-Controlled Impedance Configuration. *IEE Proceedings—Circuits, Devices and Systems*, 142, 208. http://dx.doi.org/10.1049/ip-cds:19951944

- [7] Ndjountche, T. (1996) Linear Voltage-Controlled Impedance Architecture. *Electronics Letters*, 32, 1528-1529. <u>http://dx.doi.org/10.1049/el:19961020</u>

- [8] Leuciuc, A. and Goras, L. (1998) New General Immittance Converter JFET Voltage-Controlled Impedances and Their Applications to Controlled Biquads Synthesis. *IEEE Transactions on Circuits and Systems*, 45, 678-682. <u>http://dx.doi.org/10.1109/81.678494</u>

- [9] Senani, R. (1994) Realisation of Linear Voltage-Controlled Resistance in Floating Form. Electronics Letters, 30, 1909-1911. http://dx.doi.org/10.1049/el:19941313

- [10] Senani, R. (1995) Floating GNIC/GNII Configuration Realized with Only a Single OMA. Electronics Letters, 31, 423-424. http://dx.doi.org/10.1049/el:19950287

- [11] Ndjountche, T., Unbehauen, R. and Luo, F.L. (1999) Electronically Tunable Generalized Impedance Converter Structures. International Journal of Circuit Theory and Applications, 27, 517-522.

http://dx.doi.org/10.1002/(SICI)1097-007X(199909/10)27:5<517::AID-CTA76>3.0.CO;2-Y

- [12] Maundy, B., Gift, S. and Aronhime, P. (2008) Practical Voltage/ Current Controlled Grounded Resistor with Dynamic Range Extension. IET Circuits, Devices & Systems, 2, 201-206. http://dx.doi.org/10.1049/iet-cds:20070164

- [13] Senani, R. and Bhaskar, D.R. (2008) Comment: Practical Voltage/Current Controlled Grounded Resistor with Dynamic Range Extension. IET Circuits, Devices & Systems, 2, 465-466. http://dx.doi.org/10.1049/iet-cds:20080211

- [14] Sinha, P.K., Sharma, N. and Mishra, R. (2015) A Configuration for Realizing Voltage Controlled Floating Inductance and Its Application. *Circuits and Systems*, 6, 189-199. http://dx.doi.org/10.4236/cs.2015.69020

- [15] Senani, R., Bhaskar, D.R., Singh, A.K. and Singh, V.K. (2013) Current Feedback Operational Amplifiers and Their Applications. Springer Science+ Business Media, New York, Ch. 3 Section 3.1 Introduction; First Sentence, 49.

- [16] Senani, R., Bhaskar, D.R., Gupta, S.S. and Singh, V.K. (2009) A Configuration for Realizing Floating, Linear, Voltage-Controlled Resistance, Inductance and FDNC Elements. International Journal of Circuit Theory and Applications, 37, 709-719. http://dx.doi.org/10.1002/cta.510

- [17] Chang, C.M. and Hwang, C.S. (1995) Comment on "Voltage-Mode Notch, Low Pass and Band Pass Filter Using Current-Feedback Amplifiers". Electronics Letters, 31, 246. http://dx.doi.org/10.1049/el:19950168

- [18] Senani, R. (1998) Realization of a Class of Analog Signal Processing/Signal Generation Circuits: Novel Configurations Using Current Feedback Op-Amps. Frequenz, 52, 196-206. http://dx.doi.org/10.1515/FREQ.1998.52.9-10.196

- [19] Mitra, S.K. (1969) Analysis and Synthesis of Linear Active Networks. John Wiley & Sons Inc., New York, 495.

- [20] Rikoski, R.A. and Choudhry, A. (1976) Mutator Realized Inductance. Proceedings of the IEEE, 64, 1012-1013. http://dx.doi.org/10.1109/PROC.1976.10256

- [21] Dutta Roy, S.C. (2016) A Unified Theory of Op-Amp Sinusoidal Oscillators Using Reactive  $\pi$  and T Networks in the Feedback Path. *IETE Journal of Education*, 90-95. http://dx.doi.org/10.1080/09747338.2016.1180962

### **Appendix 1: Some Appraisals**

In the context of the analysis and citations of references in [14], the following are worth pointing out for the benefit of the readers of this Journal.

1) The analysis of Section 2 at pages 192-193 of [14] is clumsy. It is well-known (for instance, see [19] [20]) that a 2-port representing floating impedance  $Z_{eq}$  is correctly characterized by either the following y-matrix [19]:

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \left(\frac{1}{Z_{eq}}\right) \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

or *equivalently*, by the following transmission matrix [20]:

| $\begin{bmatrix} v_1 \end{bmatrix}_{-}$ | 1 | $Z_{eq}$ | $\begin{bmatrix} v_2 \end{bmatrix}$ |

|-----------------------------------------|---|----------|-------------------------------------|

| $\begin{bmatrix} i_1 \end{bmatrix}^-$   | 0 | 1        | $\left\lfloor -i_{2}\right\rfloor$  |

Thus, a straight forward analysis of the circuit of **Figure 2(a)** of [14] yield its correct y-matrix as:

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \left(\frac{V_{ref}}{V_c}\right) \left(\frac{1}{sCR_1}\right) \begin{bmatrix} 1/R_2 & -1/R_2 \\ -1/R_3 & 1/R_3 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

Therefore, the circuit of **Figure 2(a)** of [14] will realize a lossless VC-FI subject to fulfillment of the condition  $R_2 = R_3$ .

On the other hand, the circuit of **Figure 3(a)** of [14] has a similar y-matrix with  $L_{eq} = CR_1R_3V_{ref}/V_c$  the condition of realization being  $R_1 = R_2$ . Therefore, the conditions  $R_2 \gg R_1$  and  $(R_1 + R_2) = R_3$  as given by the authors at page 193 of [14] for their circuit of **Figure 3(a)** are unnecessary.

2) While comparing their propositions of Figure 2(a) and Figure 3(a), the authors of [14] have cited an *unpublished work*<sup>3</sup> as reference 17, which is extremely surprising since this unpublished reference is not an open literature and was, therefore, definitely not available to the authors of [14]. In fact, this unpublished work<sup>3</sup> was quoted in the acknowledgement of reference [16] of this communication as reference 26. It is, therefore, obvious that the authors of the quoted paper [14] could have known the existence of this unpublished work (quoted as reference 17 in their paper [14]) only from the published paper [16] which curiously has not been cited by them! In view of this, reference 17 of [14] in fact, should be reference [16] of the present paper.

3) Making a Hartley oscillator using an ideal op-amp is anomalous since inductor  $L_1$ , due to being connected directly from the output of the ideal op-amp to ground, will not appear in any open loop transfer function (or loop gain) or the characteristic equation of the circuit. A resolution to this anomaly has recently been provided in [21].

<sup>&</sup>lt;sup>3</sup>Senani, R, Novel linear voltage controlled floating-impedance configurations. ELL/96/53450, dated25 November 1996, *unpublished*. The above unpublished work was cited as reference 26 in [16].

# Submit or recommend next manuscript to SCIRP and we will provide best service for you:

Accepting pre-submission inquiries through Email, Facebook, LinkedIn, Twitter, etc. A wide selection of journals (inclusive of 9 subjects, more than 200 journals) Providing 24-hour high-quality service User-friendly online submission system Fair and swift peer-review system Efficient typesetting and proofreading procedure Display of the result of downloads and visits, as well as the number of cited articles Maximum dissemination of your research work Submit your manuscript at: <u>http://papersubmission.scirp.org/</u>

Or contact cs@scirp.org