# Designs of All-Optical Higher-Order Signed-Digit Adders Using Polarization-Encoded Based Terahertz-Optical-Asymmetric-Demultiplexer (TOAD)

# Ali Hajjiah\*, Abdullah Alqallaf, Abdallah Cherri

Department of Electrical Engineering, College of Engineering & Petroleum, Kuwait University, Safat, Kuwait Email: <sup>\*</sup>ali.hajjiah@ku.edu.kw

Received 1 February 2014; revised 2 March 2014; accepted 1 April 2014

Copyright © 2014 by authors and Scientific Research Publishing Inc. This work is licensed under the Creative Commons Attribution International License (CC BY). http://creativecommons.org/licenses/by/4.0/

© Open Access

# Abstract

Various designed circuits for multiple-valued all-optical arithmetic are demonstrated. The terahertz-optical-asymmetric-demultiplexer (TOAD) switch is used as the basic structure unit in the proposed circuits due to its compact size, thermal stability, and low power operation. The designs of trinary and quaternary signed-digit numbers based adders are presented using different polarized states of light. These proposed polarization-encoded based adders use much less switches and their speeds are higher than the intensity-encoded counterparts. Further, it will be shown that one of the proposed trinary signed-digit adders is twice as fast as a recently reported modified signed-digit adder.

# Keywords

Multiple-Valued Signed-Digit, All-Optical Gates, Polarization-Encoding, Terahertz-Optical-Asymmetric-Demultiplexer (TOAD)

# **1. Introduction**

Multiple-valued logic and arithmetic is being extensively investigated as being a promising choice for future digital and optical computing [1]-[10]. Redundant signed-digit is among the various multiple-valued number systems [11]. Attractions features of this choice are higher information transmission, higher data storage *i.e.* more logic density and higher processing speed due to the opportunity of having parallel computing algorithms

<sup>\*</sup>Corresponding author.

How to cite this paper: Hajjiah, A., Alqallaf, A. and Cherri, A. (2014) Designs of All-Optical Higher-Order Signed-Digit Adders Using Polarization-Encoded Based Terahertz-Optical-Asymmetric-Demultiplexer (TOAD). *Optics and Photonics Journal*, **4**, 113-128. <u>http://dx.doi.org/10.4236/opj.2014.46012</u>

[12]. The addition/subtraction of two signed-digit numbers restricts the carry propagation to one or two adjoining digits. Many researchers proposed optoelectronics implementations to achieve fast computing arithmetic [13]-[18]. On the other hand, the recent developments in all-optical switches that are capable of demultiplexing Tb/s pulse trains push the researchers to shift towards all-optical implementations to design ultra-fast logical and arithmetic units using binary and nonbinary algorithms [19]-[24].

Recently, all-optical arithmetic operations based on terahertz-optical-asymmetric-demultiplexer (TOAD) switch were demonstrated [20] [22]. All-optical multiple logic gates (XOR, NOR, NAND) as well as binary half- and full-adders were reported using parallel TOAD structures. Further, with the help of TOAD switches, fast nonbinary adders were demonstrated [23] where the input and the control signals are all-optical in nature. The high speed is achieved due to the use of the nonlinear optical materials and the nonbinary modified signed-digit (MSD) number representation. In contrast to binary adder, the proposed circuits can be extended to n digits by employing additional stages without affecting the total addition time. Since the multiple-valued digits cannot be directly implemented using the two binary states of the TOAD switches, intensity-encoding schemes are used to transform the signed-digits into binary bits. More recently, the intensity-encoded MSD adder was improved in terms of its TOAD switches count and its speed by utilization of polarization-encoded scheme [24].

Now since multiple-valued logic/arithmetic is being viewed as an interesting approach in optical information processing, we present, in this paper, design methods to implement trinary signed-digit (TSD) and quaternary signed-digit (QSD) arithmetic. TSD and QSD number systems are represented by five and seven literals, respectively. Consequently, the two-bit intensity-encoding (light, no light) scheme, as reported in [24], cannot be used in designing the higher-order signed-digit (SD) adders. A straightforward solution is to use a three-bit intensity-encoding scheme for each SD literal. However, in this case the all-optical circuit implementation will be very complicated. Alternatively, this limitation is solved by proposing the polarized state of light (vertical and horizontal) and a two-bit encoding scheme. The polarization-encoding method is used to design fast all-optical TSD and QSD number based adders. The proposed adders are compared in terms of numbers of gate delays, TOAD switches, beam combiners, and polarization converters. Further, these circuits are compared to the previously reported MSD adder [24]. It will be shown that the TSD adder is two times faster than the MSD one; while the QSD adder speed is the same. Sections 2 and 3 will briefly review the operation of the TOAD switch and the SD number representation, respectively. Section 4 and 5 provide five adder designs: three for the TSD and two for the QSD adders. In section 6, we summarize the results and make some conclusions.

# 2. Operation of TOAD Based Optical Switch

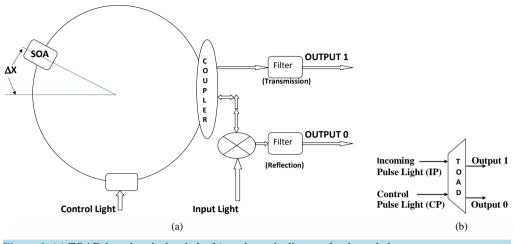

In the last few years, the TOAD switch [19] was extensively used in realizing various ultrafast logical and arithmetic operations. Its speed is due to its capability of demultiplexing tera bits per second pulse trains where a light signal controls another light beam. In addition to its speed, the relatively low power consumption makes it attractive for large-optical integration. TOAD switch consists of a loop mirror with an intra loop  $2 \times 2$  coupler and a semiconductor optical amplifier (SOA) which is offset from the loop's midpoint by a distance  $\Delta x$  as shown in **Figure 1(a)**. The SOA constitutes the nonlinear element within the switch where when exposed to a strong light it saturates and its index of refraction is changed. Full details of the operation of the TOAD switch is explained in [19] [22]. The TOAD switch operates with two lights signal through nonlinear interaction in a material based on interferometer setup: a strong optical signal, called the control pulse—*CP*, and another optical signal, called the incoming pulse—*IP*.

Briefly, the TOAD switch works as follows. When there is no CP signal, the *IP* signal enters the loop shown in **Figure 1(a)** and splits into two counter propagating ones. These two signals now recombine and interfere at the input coupler and emerge as a single light at the input port. However, if a strong *CP* light is injected into the loop causing the SOA to saturate and its index of refraction is changed. Consequently, the two *IP* counter propagating signals will face differential phase shift such that they will interfere and re-emerge or transmitted from the output port. At the two ports (reflected and transmitted), a polarization or wavelength filter is used to block the optical *CP* signal and only pass the optical *IP* signal. The energy of the optical *CP* must be sufficient to modify the optical property of the SOA element whereas the two counter propagating *IP* signals do not. Further, the *IP* and the *CP* signals are to be entered the SOA at about the same time. Further, in the absence of the *CP* signal, the input light exits from the lower port in the figure (no light is present in the upper port). However, when both CP and *IP* signals are present simultaneously, all light is directed towards the upper port because of the refractive-index change induced by the *CP* signal (no light is present in the lower port). When there is no *IP*

Figure 1. (a) TOAD-based optical switch; (b) a schematic diagram for the switch.

signal, both channels receive no light as the filter blocks the CP signal. A schematic block diagram for the TOAD switch is shown in Figure 1(b).

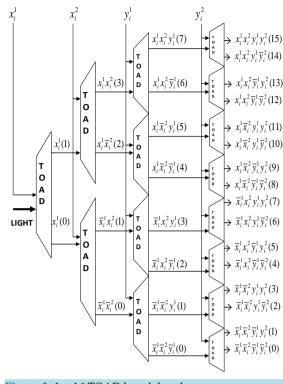

TOAD switches can successfully be used for designing logical circuits. For instance, cascaded TOAD switches as shown in **Figure 2** are used to generate the sixteen minterms for four input logical variables  $(x_i^1 x_i^2 y_i^1 y_i^2)$ . This structure can be viewed as a  $1 \times 16$  decoder where only one output is activated that corresponds to a specific minterm. Note that the output ports are numbered according to the corresponding generated minterms. *OR*ing of these minterms (sum-of-products) is performed with flexible outputs interconnectivities (beam splitters/combiners) and *ANDing* operations are achieved by cascading stages (switches) where any output port signal can be used as an input to another switch. Note that in this case, the output optical signal of the first switch may need to be amplified and/or wavelength converted before it is fed to the next switch. As a result, this switch structure can be used as a preliminary non minimized basic building block to realize any logical Boolean function.

### 3. Signed-Digit Numbers

Signed-digit (SD) numbers are formally defined as follows [12]: given a radix r, each digit of SD number assumes  $(2\alpha + 1)$  values of the digit set  $\{-\alpha, \dots, -1, 0, 1, \dots, \alpha\}$  where  $\alpha \le r - 1$  and  $r \ge 3$ . In general, a decimal number D may be represented in terms of an *n*-digits SD number as

$$D = \sum_{j=0}^{n-1} b_j r^j \tag{1}$$

where  $b_i$  digit is selected from the set  $\{-\alpha, \dots, -1, 0, 1, \dots, \alpha\}$  to produce the appropriate decimal representation. For trinary signed-digit (TSD) r = 3, the digit set is  $\{\overline{2}, \overline{1}, 0, 1, 2\}$ ; whereas for quaternary signed-digit (QSD) r = 4 and the digit set is  $\{\overline{3}, \overline{2}, \overline{1}, 0, 1, 2, 3\}$ . Here the digits  $\overline{3}, \overline{2}$ , and  $\overline{1}$  denote -3, -2, and -1, respectively.

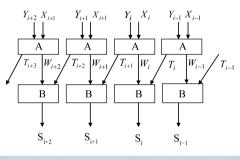

For radix  $\geq$  3, the addition operation of two SD numbers is performed in two successive steps because some digit combinations cause carry propagation to the next higher-order digit. The generation of a carry may be avoided by mapping the two SD digits in question into an intermediate sum and an intermediate carry (also known as weight and transfer digits) such that the *i*-th intermediate sum and the (*i*-1)-th intermediate carry when added generate no carry. The two-step addition is governed by the following equations:

Step-one

$$\rightarrow X_i + Y_i = rT_{i+1} + W_i$$

(2)

$$\text{Step-two} \to S_i = T_i + W_i \tag{3}$$

where  $T_i$  and  $W_i$  represent the intermediate carry and sum, respectively, and  $S_i$  is the final carry-free sum. Further, subtraction of two SD numbers can be obtained by first complementing the subtrahend and then an addition operation is applied. Thus, the subtraction of two SD numbers involves three steps.

Figure 2.  $1 \times 16$  TOAD based decoder.

The totally-parallel adder for SD number representation is shown in Figure 3 where the functional blocks A and B represent the computing rules generated from Equations (2) and (3), respectively.

For TSD and QSD numbers, all possible two SD numbers that satisfy Equations (2) and (3) above are listed in **Table 1** and **Table 2**, respectively. Note that the SD numbers in these tables are grouped according to the value of the output digit. The pairs of the to-be-added trinary digits are first divided into nine groups (for the first step) as shown in the second column of Table 1a whereas the third column of the table shows the necessary intermediate carry and intermediate sum digits for carry-free addition. **Table 1(b)** lists the rules for the second step of the addition. Thus, **Table 1(a)** and **Table 1(b)** represent the 25 and the 9 computational rules that are used in blocks **A** and **B** of **Figure 3** for the TSD addition. Notice that these tables include polarization encoding of the SD digits that will be explained in the next section.

Similarly, the pairs of the to-be-added quaternary digits are arranged into thirteen groups for the first step and seven groups for the second step as shown in Table 2.

## 4. Polarization-Encoded TOAD-Based TSD Adder Circuits

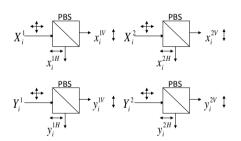

It was mentioned in the previous section that the TOAD-based decoder method can be used to implement any logical function expressed as sum-of-products. The variables of the minterms are the control signals of the decoder. Now, since the TSD numbers { $\overline{2}$ ,  $\overline{1}$ , 0, 1, 2} have five symbols, a three-bit intensity-encoding scheme (light, no light) is needed for each SD symbol to provide the control signals. Therefore, the addition of two SD numbers requires six control signals. Consequently, the design of the all-optical circuit requires  $1 \times 64$  decoder with tens of TOAD switches. Obviously, this is not practical. As a solution to this limitation we propose using polarized state of light (vertical and horizontal) and a two-bit encoding scheme such that the TSD numbers { $\overline{2}$ ,  $\overline{1}$ , 0, 1, 2} are encoded as {H0, 0H, 00, 0V, V0}, respectively. Further, recall that the light of the two inputs in a TOAD switch (the CP and the IP lights) must have different intensities, different wavelengths, or different light polarization states. Since we do not know the polarization state of the light representing the TSD number ahead of time, then we cannot feed this light signal to the decoder as a control signal. This difficulty can be solved by using polarization beam splitters in order to generate two polarization channels for each TSD digits. Therefore, a TSD digit  $X_i$ , which is decoded as  $X_i = x_i^1 x_i^2$ , is routed to polarization beam splitters (PBS) to produce

| (a)             |                                                                                                                                                                                                         |                                                              |                                           |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|--|

| Group<br>Number | Addend/Au<br>$x_i y_i \left( x_i^{1H} x_i^{2H} y_i^{1H} y_i^{2H} \right)$                                                                                                                               | agend<br>$x_i^{1V} x_i^{2V} y_i^{1V} y_i^{2V} \right)$       | Intermediate<br>Carry/Sum<br>$T_{i+1}W_i$ |  |

| G1              | 2 2 (0 0 0 0                                                                                                                                                                                            | V 0 V 0)                                                     | 11 (V V)                                  |  |

| G2              | 21 (0000<br>12 (0000                                                                                                                                                                                    | V 0 0 V)<br>0 V V 0)                                         | 10 (V0)                                   |  |

| G3              | $\begin{array}{cccccccc} 1 & 1 & (0 & 0 & 0 & 0 \\ 0 & 2 & (0 & 0 & 0 & 0 \\ 2 & 0 & (0 & 0 & 0 & 0 \end{array}$                                                                                        | 0 V 0 V)<br>0 0 V 0)<br>V 0 0 0)                             | 1 1 (V H)                                 |  |

| G4              | $\begin{array}{c} 0 \ 1 & (0 \ 0 \ 0 \ 0 \\ 1 \ 0 & (0 \ 0 \ 0 \ 0 \\ 2 \ \overline{1} & (0 \ 0 \ 0 \ H \\ \overline{1} \ 2 & (0 \ H \ 0 \ 0 \\ \end{array}$                                            | 0 0 0 V)<br>0 V 0 0)<br>V 0 0 0)<br>0 0 V 0)                 | 01 (0V)                                   |  |

| G5              | $\begin{array}{cccc} 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & \overline{1} & 0 & 0 & 0 & H \\ \hline 1 & 1 & 0 & H & 0 & 0 \\ 2 & \overline{2} & 0 & 0 & H & 0 \\ \hline 2 & 2 & (H & 0 & 0 & 0 & 0 \\ \end{array}$ | 0 0 0 0)<br>0 V 0 0)<br>0 0 0 V)<br>V 0 0 0)<br>0 0 V 0)     | 0 0 (0 0)                                 |  |

| G6              | $\begin{array}{cccc} \overline{2} & 1 & (H & 0 & 0 & 0 \\ 1 & \overline{2} & (0 & 0 & H & 0 \\ 0 & \overline{1} & (0 & 0 & 0 & H \\ \hline 1 & 0 & (0 & H & 0 & 0 \end{array}$                          | 0 0 0 V)<br>0 V 0 0)<br>0 0 0 0)<br>0 0 0 0)                 | 0 1 (0 H)                                 |  |

| G7              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                   | $\begin{array}{c} 0 \ 0 \ 0 \ 0 \\ 0 \ 0 \ 0 \ 0 \\ 0 \ 0 \$ | 1 1 (H V)                                 |  |

| G8              | $\frac{\overline{1}}{\overline{2}} \frac{\overline{2}}{\overline{1}} (0 \text{ H H } 0) $                                                                                                               | 0 0 0 0)<br>0 0 0 0)                                         | ī 0 (H 0)                                 |  |

| G9              | $\overline{2}$ $\overline{2}$ (H 0 H 0                                                                                                                                                                  | 0000)                                                        | $\overline{1} \ \overline{1} \ (H H)$     |  |

|                 | a                                                                                                                                                                                                       |                                                              |                                           |  |

Table 1. (a) Truth table and polarization-encoding for the first step TSD addition; (b) Truth table and polarization-encoding for the second TSD addition.

|                 | (b)                                                                                        |                                             |

|-----------------|--------------------------------------------------------------------------------------------|---------------------------------------------|

| Group<br>Number | Intermediate Carry/Sum<br>$T_i W_i \left(T_i^H T_i^V W_i^H W_i^V\right)$                   | Final Sum<br>$S_i \left(S_i^1 S_i^2\right)$ |

| G1              | 11 (0V0V)                                                                                  | 2 (V 0)                                     |

| G2              | 0 1 (000V)<br>1 0 (0V00)                                                                   | 1 (0 V)                                     |

| G3              | 0 0 (0000)<br>1 Ī (0VH0)<br>Ī 1 (H00V)                                                     | 0 (0 0)                                     |

| G4              | $ \begin{array}{rcrc} 0 \ \overline{1} & (00H0) \\ \overline{1} \ 0 & (H000) \end{array} $ | ī (0 H)                                     |

| G5              | 1 1 (H0H0)                                                                                 | 2 (H 0)                                     |

$X_i = x_i^{1H} x_i^{2H} x_i^{1V} x_i^{2V}$  as shown in **Figure 4**. This encoding scheme is used for the addend and the augend for the TSD numbers in **Table 1** and **Table 2**. Further, whenever the intermediate carry or the intermediate sum digit in the adder belongs to the set { $\overline{1}$ , 0, 1}, one-bit encoding such as {H, 0, V} is used in the encoding scheme.

Table 2. (a) Truth table and polarization-encoding for the first step

QSD addition; (b) Truth table and polarization-encoding for the

second step QSD addition.

| (a)    |                                                                                                          |                                        |                                                                  |  |

|--------|----------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------|--|

| Group  | Addend/Augend                                                                                            |                                        | Intermediate Carry/Sum                                           |  |

| Number | $x_i y_i \left( x_i^{1H} x_i^{2H} y_i^{1H} y_i^{2H} \right)$                                             | $x_i^{1V} x_i^{2V} y_i^{1V} y_i^{2V}$  | $T_{i+1}W_i\left(t_{i+1}W_i^{1V}W_i^{2V}W_i^{1H}W_i^{2H}\right)$ |  |

| G1     | 33 (0000                                                                                                 | V V V V)                               | 12 (V V000)                                                      |  |

| G2     | 23 (0000                                                                                                 | V 0 V V)                               | 11 (V 0V00)                                                      |  |

|        | 32 (0000                                                                                                 | V V V 0)                               | 11 (* 0*00)                                                      |  |

|        | 31 (0000                                                                                                 | V V 0 V)                               |                                                                  |  |

| G3     | 13 (0000                                                                                                 | 0 V V V                                | 10 (V 0000)                                                      |  |

|        | $   \begin{array}{r}     2 2 (0 0 0 0 \\     2 1 (0 0 0 0 \\   \end{array} $                             | V 0 V 0)<br>V 0 0 V)                   |                                                                  |  |

|        | 12 (0000)                                                                                                | 0 V V 0)                               |                                                                  |  |

| G4     | 03 (0000                                                                                                 | 0 0 V V)                               | $1 \overline{1} (V 0 0 0 H)$                                     |  |

|        | 30 (0000                                                                                                 | V V 0 0)                               |                                                                  |  |

|        | 11 (0000                                                                                                 | 0 V 0 V)                               |                                                                  |  |

|        | 0 2 (0 0 0 0                                                                                             | 00V0)                                  |                                                                  |  |

| G5     | 20 (0000                                                                                                 | V 0 0 0)                               | 02 (0 V0 00)                                                     |  |

|        | 3 1 (0 0 0 H                                                                                             | V V 0 0)                               |                                                                  |  |

|        | <u>1</u> 3 (0 H 0 0                                                                                      | 00VV)                                  |                                                                  |  |

|        | 01 (0000                                                                                                 | 000V)                                  |                                                                  |  |

|        | 10(0000)                                                                                                 | 0 V 0 0)                               |                                                                  |  |

| G6     | 2 1 (0 0 0 H                                                                                             | V 0 0 0)                               | 01 (0 0V00)                                                      |  |

|        | $\overline{1}$ 2 (0 H 0 0                                                                                | 0 0 V 0)                               | (                                                                |  |

|        | $3\overline{2}$ (00H0                                                                                    | V V 0 0)                               |                                                                  |  |

|        | <u>2</u> 3 (H 0 0 0                                                                                      | $\frac{00 \text{ V V}}{000 \text{ O}}$ |                                                                  |  |

|        | 00 (0000)                                                                                                | 0000)                                  |                                                                  |  |

|        | $\begin{array}{ccc} 1 \overline{1} & (0 \ 0 \ 0 \ H \\ \overline{1} \ 1 & (0 \ H \ 0 \ 0 \\ \end{array}$ | 0 V 0 0                                |                                                                  |  |

| G7     | $2\overline{2}$ (00H0<br>2 $\overline{2}$ (00H0                                                          | 0 0 0 V)<br>V 0 0 0)                   | 00(00000)                                                        |  |

| 07     | $\frac{2}{2}$ (00000<br>$\frac{1}{2}$ 2 (H000                                                            | 0 0 V 0)                               |                                                                  |  |

|        | $\overline{3}$ 3 (HH00                                                                                   | 00V0)                                  |                                                                  |  |

|        | $3\overline{3}$ (00HH                                                                                    | V V 0 0)                               |                                                                  |  |

|        | $0\overline{1} (000 \mathrm{H})$                                                                         | 0000)                                  |                                                                  |  |

|        | $\overline{1}$ 0 (0 H 0 0                                                                                | 0000)                                  |                                                                  |  |

|        | $\overline{2}$ 1 (H 0 0 0                                                                                | 000V)                                  | _                                                                |  |

| G8     | $1\overline{2}$ (00H0                                                                                    | 0 V 0 0)                               | $0 \overline{1} (0 \ 0 \ 0 \ 0 \ H)$                             |  |

|        | $\overline{3}2$ (HH00                                                                                    | 00V0)                                  |                                                                  |  |

|        | $2\overline{3}$ (00 H H                                                                                  | V 0 0 0)                               |                                                                  |  |

|        | <u>1</u> <u>1</u> (0H0H                                                                                  | 0000)                                  |                                                                  |  |

|        | $0 \overline{2} (0 0 H 0)$                                                                               | 0000)                                  |                                                                  |  |

| G9     | $\overline{2}$ 0 (H 0 0 0                                                                                | 0000)                                  | $0 \overline{2} (0 00 H 0)$                                      |  |

|        | $\overline{3}$ 1 (H H 0 0                                                                                | 000V)                                  |                                                                  |  |

|        | 1 3 (0 0 H H                                                                                             | 0 V 0 0)                               |                                                                  |  |

|        | $\overline{1} \overline{2} (0 H H 0)$                                                                    | 0000)                                  |                                                                  |  |

| G10    | $\overline{2}$ $\overline{1}$ (H 0 0 H                                                                   | 0000)                                  | $\overline{1}$ 1 (U 0 V 0 0)                                     |  |

|        | $\overline{3}$ 0 (H H 0 0                                                                                | 0000)                                  | $\overline{1}$ 1 (H 0 V 0 0)                                     |  |

|        | 0 3 (0 0 H H                                                                                             | 0000)                                  |                                                                  |  |

|        | 31 (H H 0 H                                                                                              | 0000)                                  |                                                                  |  |

| G11    | $\overline{1}$ $\overline{3}$ (0 H H H                                                                   | 0000)                                  | $\overline{1} 0 (H 0 0 0 0)$                                     |  |

|        | $\overline{2} \ \overline{2} \ (H \ 0 \ H \ 0$                                                           | 0000)                                  |                                                                  |  |

| G12    | 37 (H H H 0                                                                                              | 0000)                                  | <u>.</u>                                                         |  |

|        | 23 (H0HH                                                                                                 | 0000)                                  | $\overline{1}$ $\overline{1}$ (H 000 H)                          |  |

| G13    | 33 (H H H H                                                                                              | 0000)                                  | $\overline{1}$ $\overline{2}$ (H 00H0)                           |  |

|        |                                                                                                          |                                        |                                                                  |  |

|                 | (b)                                                                                             |                                               |

|-----------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Group<br>Number | Intermediate Carry/Sum<br>$T_i W_i \left(T_i^H T_i^V w_i^{IV} w_i^{2V} w_i^{H} w_i^{2H}\right)$ | Final Sum<br>$S_i \left( S_i^1 S_i^2 \right)$ |

| G1              | 12 (0 V V 0 0 0)                                                                                | 3 (V V)                                       |

| G2              | 1 1 (0 V 0 V 0 0)                                                                               | 2 (V 0)                                       |

| G3              | 0 1 (0 0 0 V 0 0)<br>1 0 (0 V 0 0 0 0)                                                          | 1 (0 V)                                       |

| G4              | 0 0 (0 0 0 0 0 0)<br>1 1 (0 V 0 0 0 H)<br>1 1 (H 0 0 V 0 0)                                     | 0 (0 0)                                       |

| G5              | 0 1 (0 0 0 0 0 H)<br>1 0 (H 0 0 0 0 0)                                                          | 1 (0 H)                                       |

| G6              | ī ī (H 0 0 0 0 H)                                                                               | 2 (H 0)                                       |

| G7              | $\overline{1} \ \overline{2} \ (H \ 0 \ 0 \ 0 \ H \ 0)$                                         | 3 (H H)                                       |

Figure 4. Two-bit polarization-encoding of the multiple-valued SD digits.

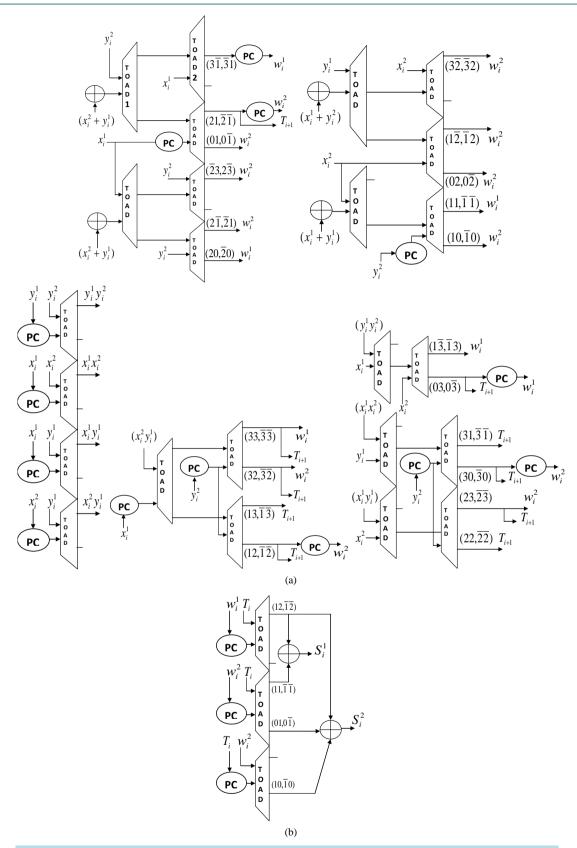

#### 4.1. TSD: DESIGN1

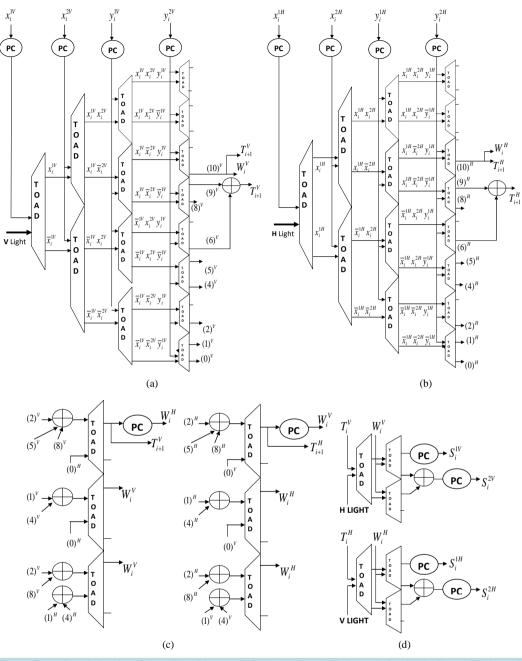

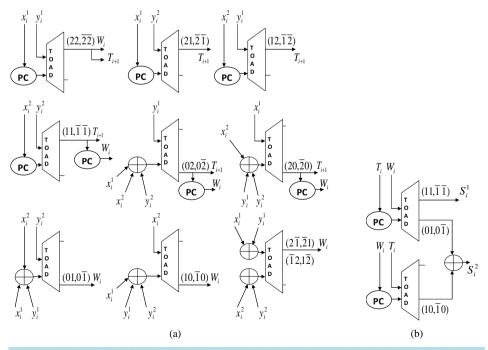

The TSD addition is a two-step process where the first step generates an intermediate transfer  $T_{i+1}$  digit and an intermediate weight  $W_i$  digit that do not have the symbols  $\overline{2}$  and 2; whereas the second step adds the digits  $T_i$  and  $W_i$  to produce the final sum. **Table 1** lists the  $\langle H, V \rangle$  polarization-encoding of the two-step TSD addition. Studying **Table 1(a)** reveals that the minterms can be divided into three parts: (i) one group of minterms (the first eight entries) that have only V symbols; (ii) s second group of minterms (entries eighteen to twenty five) that have only H symbols; and (iii) a third group of minterms that have mixed V and H symbols. Therefore, a straight forward design method is to construct three channels or circuits to combine these minterms and produce the corresponding  $T_{i+1}W_i$  digit outputs using the  $1 \times 16$  decoder as the basic building block. **Figure 5** (b) illustrate the V-channel and the H-channel circuits, respectively; while the circuit in **Figure 5(c)** takes some outputs of the V- and the H-channel and combine them in order to produce the corresponding  $T_{i+1}W_i$  digits. Note that the output of the  $1 \times 16$  decoders in these circuits are denoted by numbers in parentheses with a superscript letter

Figure 5. Designed circuits of the TSD adder: DESIGN1: (a) Step 1 *V*-channel circuit; (b) Step 1 *H*-channel; (c) Step 1 *HV*-channel circuit; and (d) Step 2 circuit.

representing the polarization state. Figure 5(d) represents the designed circuit for the second step (Table 1(b)) of the adder that generates the sum digits. In this figure, a simplified  $1 \times 4$  decoder is used. This adder design requires only 36 switches and it takes seven gate delay units for the addition. Note that this is a non-minimized TSD adder design, which can be improved by reducing both the numbers of TOAD switches and the delay units. Further, polarization converters (PC) are used before the control signals and continuous light sources are needed for the circuit to work properly.

## 4.2. TSD DESIGN2

This subsection demonstrates a second design method for the TSD adder which is not based on the  $1 \times 16$

TOAD decoder. When a closer look at the polarization-encoded TSD digits of **Table 1(a)** is carried out, it is observed that when the signals  $(x_i^{1H}, x_i^{2H}, y_i^{1H}, y_i^{2H})$  are combined and produced no light output, then this indicates the *V*-channel entries in the table. In a similar way, the signals  $(x_i^{1V}, x_i^{2V}, y_i^{1V}, y_i^{2V})$  indicate the *H*-channel entries of the truth table. Now, the combined signals of  $(x_i^{1V}, x_i^{2V}, y_i^{1V}, y_i^{2V})$  can be used as *IP* input and the combined signals  $(x_i^{1H}, x_i^{2H}, y_i^{1H}, y_i^{2H})$  can be used as *CP* input in one TOAD switch; while they can be used as *CP* and *IP* inputs in a second TOAD switch as illustrated in **Figure 6(a)** and **Figure 6(b)**. This same method is used to distinguish the mix polarization channel as shown in **Figure 6(c)**.

Figure 6. Designed circuits of the TSD adder: DESIGN2: (a) Step 1 V-channel circuit; (b) Step 1 H-channel; (c) Step 1 HV-channel circuit; and (d) Step 2 circuit.

On the other hand, the second step of the TSD adder is redesigned in order to eliminate the continuous H- and V-light sources in the circuits and at the same time maintain the same numbers of TOAD switches and the delay units as demonstrated in **Figure 6(d)**. Furthermore, to clarify the generated outputs of each TOAD switch in the circuit, we posted the corresponding minterms at the output ports. This design method resulted in a better and a faster adder than DESIGN1. Thus, DESIGN2 requires only 24 gates and it takes only four gate delay units for the addition. Note that this design needs more beam combiners.

#### 4.3. TSD DESIGN3

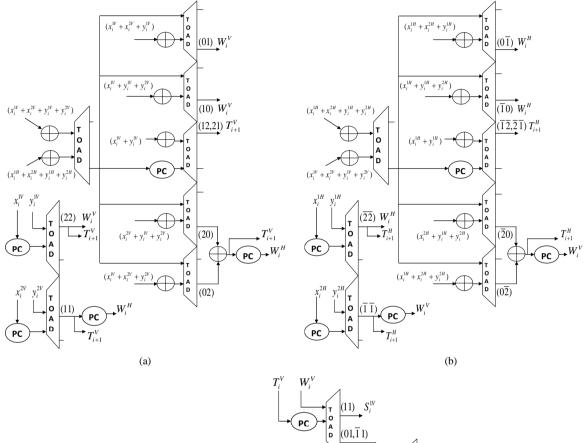

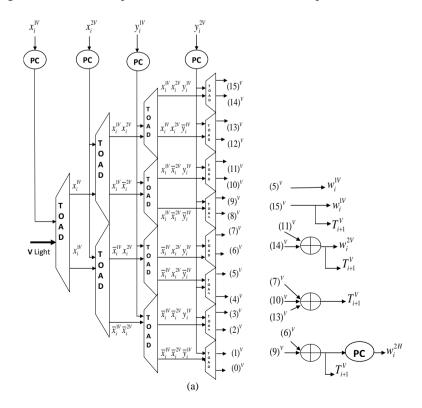

This proposed design method avoids using the  $1 \times 16$  TOAD decoder, the polarization beam splitters that generate the *H*- and the *V*-channels, and the continuous *H*- and *V*-light sources. The TSD numbers { $\overline{2}$ ,  $\overline{1}$ , 0, 1, 2} are encoded by two digits  $X_i = x_i^1 x_i^2$  as {*H*0, 0*H*, 00, 0*V*, *V*0}. This imposes on the designer to carefully consider the state polarizations of both the control and the incoming pulse signals (*CP* and *IP*) for every possible combination digits of the TSD adder. In this regard, every signal in the TOAD switch (being an input or an output signal) has a trinary representation *i.e.* the signal can have vertically polarized, horizontally polarized, or no light. Exhaustive considerations of  $x_i^1$ ,  $x_i^2$ ,  $y_i^1$ ,  $y_i^2$  or any combinations of these digits as being either *CP* or *IP* inputs along with polarization conversion, lead to DESIGN3 as shown in **Figure 7**. Again in this figure, the minterms of the adder of **Table 1** are posted at the outputs of every TOAD switch. A huge improvement is achieved in this design since the number of gates is reduced by 70% to 11 and the delay is reduced by 72% to 2 units.

## 5. Polarization-Encoded TOAD-Based QSD Adder Circuits

The quaternary literals { $\overline{3}$ ,  $\overline{2}$ ,  $\overline{1}$ , 0, 1, 2, 3} need a three-bit intensity encoding (light, no light encoding) for each signed-digit representation. However, a two-bit scheme is sufficient to represent the seven symbols when polarization-encoding is used such as { $\overline{3} = HH$ ,  $\overline{2} = HO$ ,  $\overline{1} = OH$ , 0 = OO, 1 = OV, 2 = VO, 3 = VV HH}. In a similar manner to the TSD adder, the QSD addition is a two-step process where the first step generates an intermediate transfer  $T_{i\pm 1}$  digit that belongs to the set { $\overline{1}$ , 0, 1} and an intermediate weights  $W_i$  digit that belongs to the set { $\overline{2}$ ,  $\overline{1}$ , 0, 1, 2}; whereas the second step adds the digits  $T_i$  and  $W_i$  to produce the final sum. Therefore, a single polarized bit can be used to represent the transfer digits  $T_{i+1}$  while two polarized-bit are needed to represent the weight digits  $W_i$ .

Figure 7. Designed circuits of the TSD adder: DESIGN3: (a) Step 1 circuit; (b) Step 2 circuit.

#### 5.1. QSD DESIGN1

This design uses the same approach as for DESIGN1 of the TSD adder where the  $1 \times 16$  TOAD decoder constitutes the core part of the design. In this regard, polarization beam splitters are needed to generate the appropriate polarized *CP*. **Table 2** lists the *<H,V>* polarization encoding of the two-step QSD addition. Again, the entries in the table are classified as three groups that have only *V* symbols, only *H* symbols, and mixed *HV* symbols. Accordingly, the adder is designed in a straight forward manner and divided into three channels. The combinations of output digits of these channels will produce the appropriate sum. **Figure 8** illustrates the circuit for this QSD adder. As it is expected, the circuit is more complicated having 54 TOAD switches and it takes eight gate delay units for the addition.

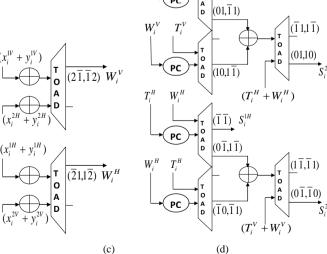

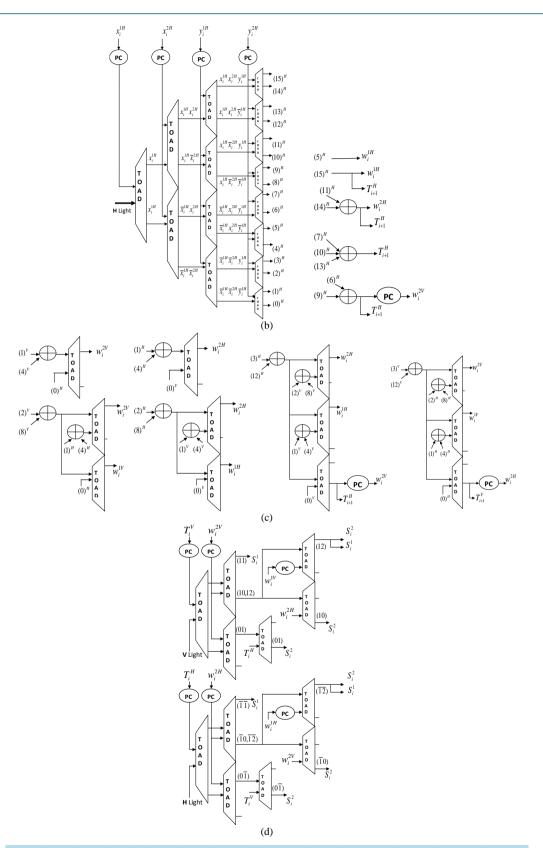

#### 5.2. QSD DESIGN2

It can be shown that by following a similar procedure to that of DESIGN2 of the TSD adder of the previous section, a better and reduced number of gate count for the QSD adder can be obtained. However, in this subsection we will provide a much better QSD adder, which follows the design method used in DESIGN3 of the TSD adder. **Figure 9** presents this design where the nonzero outputs of the minterms (the entries in **Table 2**) are realized individually and they are shown at the output ports of the TOAD switches. To illustrate the working mechanisms of this design, let us consider generating the output for the minterms  $3\overline{1}$ , which is encoded as

$x_i^1 x_i^2 y_i^1 y_i^2 = VV0H$ . This minterms is obtained using the circuit in the upper left corner in **Figure 9(a)**. The input light to TOAD1 is  $y_i^2 = H$  and the control signal is  $(x_i^2 + y_i^1) = V$ . Thus the upper port of TOAD1 will have *H*-light and it is used as input signal to TOAD2. Since the control signal of TOAD2 is  $x_i^1 = V$ , then the upper port of TOAD2 will have *H*-light, which is polarization converted to generate *V*-light as it is required. In a similar way, we can obtain the output of the minterm  $\overline{31}$ . This QSD adder is denoted as DESIGN2 where the size is reduced by one half and the speed is increased by a factor of two compared to QSD DESIGN1 adder. The designed circuit requires only 27 gates and it takes four gate delay units for the addition.

## **6.** Conclusions

In this paper, designs of ultra-fast all-optical TOAD-based adders for multiple-valued SD numbers are reported.

Figure 8. Designed circuits of the QSD adder: DESIGN1: (a) Step 1 *V*-channel circuit; (b) Step 1 *H*-channel circuit; (c) Step 1 *HV*-channel circuit; and (d) Step 2 circuit.

Figure 9. Designed circuits of the QSD adder: DESIGN2: (a) Step 1 circuit and (b) Step 2 circuit.

| Table 5. Comparison between the multiple valued SD circuit designs. |         |            |             |                |                         |

|---------------------------------------------------------------------|---------|------------|-------------|----------------|-------------------------|

| Adder                                                               |         | Unit delay | Gates count | Beam combiners | Polarization converters |

| TSD                                                                 | DESIGN1 | 7          | 36          | 14             | 14                      |

|                                                                     | DESIGN2 | 4          | 24          | 26             | 12                      |

|                                                                     | DESIGN3 | 2          | 11          | 9              | 9                       |

| QSD                                                                 | DESIGN1 | 8          | 54          | 20             | 18                      |

|                                                                     | DESIGN2 | 4          | 27          | 8              | 17                      |

| MSD                                                                 | DESIGN2 | 4          | 10          | 11             | 7                       |

|                                                                     |         |            |             |                |                         |

Table 3. Comparison between the multiple valued SD circuit designs.

These adders can be used as subtracters units once the augends are complemented and used as input digits to the designed adders. Three TSD (two QSD) circuits are designed and demonstrated. **Table 3** summarizes the design elements of the proposed TSD and QSD adders as well as the most recently proposed MSD adder [24]. From this table, we can see that the QSD adder (DESIGN2) has the same speed (unit delay) as for the MSD adder while the gates count is higher as expected. Thus, this makes the proposed QSD adder an attractive circuit candidate knowing that the QSD number system (7 literals) provides more transmission information and more storage density than the MSD number system (3 literals).

On the other hand, the TSD adder (DESIGN3) is two times faster than both the QSD and the MSD counterparts. While the TSD gates count is almost the same as for the MSD adder and about 60% less than the QSD adder. Consequently, these results make the TSD adder very attractive and a good candidate for future considerations in digital optical computing.

It is worth mentioning that the previous proposed designs are theoretical. However, many theoretical simulations of similar TOAD-based circuits that prove their feasibilities were reported [25]-[28]. In addition, many reported works using TOAD switches demonstrated results with simulations using practical parameters or results from laboratories experimental data. Furthermore, note that when implementing multistage interconnection circuits using TOADs as the basic switch, one has to be aware of many practical issues such as synchronization and cascadability in addition to light intensity losses due to splitters/combiners, polarization, pulse duration, noise and others related issues [29]-[33].

#### References

- Lakshmi, B. and Dhar, A.S. (2013) VLSI Architecture for Parallel Radix-4 CORDIC. *Microprocessors and Microsystems*, 37, 79-86. <u>http://dx.doi.org/10.1016/j.micpro.2012.12.001</u>

- [2] Nikmehr, H., Phillips, B. and Lim, C.C. (2010) A Novel Implementation of Radix-4 Floating-Point Division/Square-Root Using Comparison Multiples. *Computers & Electrical Engineering*, **36**, 850-863. http://dx.doi.org/10.1016/j.compeleceng.2008.04.013

- Ruiz, G.A. and Granda, M. (2011) Efficient Canonic Signed Digit Recoding. *Microelectronics Journal*, 42, 1090-1097. http://dx.doi.org/10.1016/j.mejo.2011.06.006

- [4] Jaberipur, G. and Gorgin, S. (2010) An Improved Maximally Redundant Signed Digit Adder. Computers & Electrical Engineering, 36, 491-502. <u>http://dx.doi.org/10.1016/j.compeleceng.2009.12.002</u>

- [5] Cherri, A.K. and Alam, M.S. (2000) Parallel Computation of Complex Elementary Functions Using Quaternary Signed-Digit Arithmetic. Optics & Laser Technology, 32, 391-399. <u>http://dx.doi.org/10.1016/S0030-3992(00)00103-1</u>

- [6] Alam, M.S. (1994) Parallel Optical Computing Using Recoded Trinary Signed-Digit Numbers. Applied Optics, 33, 4392-4397. <u>http://dx.doi.org/10.1364/AO.33.004392</u>

- [7] Chattopadhyay, T. (2010) All-Optical Quaternary Circuits Using Quaternary T-Gate. *Optik*, **121**, 1784-1788. <u>http://dx.doi.org/10.1364/AO.33.004392</u>

- [8] Chattopadhyay, T. (2010) All-Optical Symmetric Ternary Logic Gate. Optics & Laser Technology, 42, 1014-1021. http://dx.doi.org/10.1016/j.optlastec.2010.01.023

- [9] Cherri, A.K. and Al-Zayed, A. (2010) Circuits Designs of Ultra-Fast All-Optical Modified Signed-Digit Adders Using Semiconductor Optical Amplifier and Mach-Zehnder Interferometer. *Optik*, **121**, 1577-1585. http://dx.doi.org/10.1016/j.ijleo.2009.02.029

- [10] Ghosh, A.K., Bhattacharya, A., Raul, M. and Basuray, A. (2012) Trinary Arithmetic and Logic Unit (TALU) Using Savart Plate and Spatial Light Modulator (SLM) Suitable for Optical Computation in Multivalued Logic. Optics & La-

ser Technology, 44, 1583-1592. http://dx.doi.org/10.1016/j.optlastec.2011.11.044

- [11] Avizienis, A. (1961) Signed-Digit Number Representations for Fast Parallel Arithmetic. IRE Trans Electronic Computers, EC-10, 89-400.

- [12] Hwang, K. (1979) Computer Arithmetic Principles: Architecture and Design. WILEY Publishing Co., New York.

- [13] Cherri, A.K. and Khachab, N.I. (1996) Canonical Quaternary Signed-Digit Arithmetic Using Optoelectronics Symbolic Substitution. Optics & Laser Technology, 28, 397-403. <u>http://dx.doi.org/10.1016/0030-3992(95)00109-3</u>

- [14] Awwal, A.A.S. (1993) Recoded Signed-Digit Binary Addition-Subtraction Using Optoelectronic Symbolic Substitution. Applied Optics, 31, 3205-3208. <u>http://dx.doi.org/10.1364/AO.31.003205</u>

- [15] Ha, B. and Li, Y. (1994) Parallel Modified Signed-Digit Arithmetic Using an Optoelectronic Shared Content-Addressable-Memory Processor. Applied Optics, 33, 3647-3662. <u>http://dx.doi.org/10.1364/AO.33.003647</u>

- [16] Huang, H.X., Itoh, M., Yatagai, T. and Liu, L.R. (1996) Classified One-Step Modified Signed-Digit Arithmetic and Its Optical Implementation. *Optics Engineering*, 35, 1134-1140. <u>http://dx.doi.org/10.1117/1.600602</u>

- [17] Qian, F., Li, G., Ruan, H. and Liu, L. (1999) Modified Signed-Digit Addition by Using Binary Logic Operations and Its Optoelectronic Implementation. *Optics & Laser Technology*, **31**, 403-410. <u>http://dx.doi.org/10.1016/S0030-3992(99)00078-X</u>

- [18] Nishimura, N., Awatsuji, Y. and Kubota, T. (2004) Two-Dimensional Arrangement of Spatial Patterns Representing Numerical Data in Input Images for Effective Use of Hardware Resources in Digital Optical Computing System Based on Optical Array Logic. *Journal of Parallel and Distributed Computing*, 64, 1027-1040. <u>http://dx.doi.org/10.1016/j.jpdc.2004.06.011</u>

- [19] Sokoloff, J.P., Prucnal, P.R., Glesk, I. and Kane, M. (1993) A Terahertz Optical Asymmetric Demultiplexer (TOAD). *IEEE Photonics Technology Letters*, 5, 787-789. <u>http://dx.doi.org/10.1109/68.229807</u>

- [20] Wang, B.C., Baby, V., Tong, W., Xu, L., Friedman, M., Runser, R.J., Glesk, I. and Prunchal, P.R. (2002) A Novel Fast Optical Switch Based on Two Cascaded Terahertz Asymmetric Demultiplexers (TOAD). *Optics Express*, 10, 15-23. http://dx.doi.org/10.1364/OE.10.000015

- [21] Gayen, D. and Roy, J.N. (2008) All-Optical Arithmetic Unit with the Help of Terahertz-Optical-Asymmetric-Demultiplexer-Based Tree Architecture. *Applied Optics*, 47, 933-943. <u>http://dx.doi.org/10.1364/AO.47.000933</u>

- [22] Roy, J.N. and Gayen, D.K. (2007) Integrated All-Optical Logic and Arithmetic Operations with the Help of a TOAD Based Interferometer Device-Alternative Approach. *Applied Optics*, **46**, 5304-5310. http://dx.doi.org/10.1364/AO.46.005304

- [23] Cherri, A.K. (2010) Terahertz-Optical-Asymmetric-Demultiplexer (TOAD)-Based Arithmetic Units for Ultra-Fast Optical Information Processing. SPIE Proceedings, 7671.

- [24] Alqallaf, A.K., Hajjiah, A.T. and Cherri, A.K. (2013) Ultra-Fast All-Optical Polarization-Encoded Modified Signed-Digit Addition Using Terahertz-Optical-Asymmetric-Demultiplexer (TOAD) Switches. *Optik*, **124**, 4887-4891. http://dx.doi.org/10.1016/j.ijleo.2013.02.028

- [25] Minh, H.L., Ghassemlooy, Z. and Ng, W.P. (2008) Characterization and Performance Analysis of a TOAD Switch Employing a Dual Control Pulse Scheme in High-Speed OTDM Demultiplexer. *IEEE Communications Letters*, 12, 316-318. http://dx.doi.org/10.1109/LCOMM.2008.061299

- [26] Zoiros, K.E., Das, M.K., Gayen, D.K., Maity, H.K., Chattopadhyay, T. and Roy, J.N. (2011) All-Optical Pseudorandom Binary Sequence Generator with Toad-Based D Flip-Flops. *Optics Communications*, 284, 4297-4306. http://dx.doi.org/10.1016/j.optcom.2011.05.007

- [27] Gayen, D.K., Roy, J.N. and Pal, R.K. (2012) All-Optical Carry Lookahead Adder with the Help of Terahertz-Optical-Asymmetric-Demultiplexer. Optik, 123, 40-45. <u>http://dx.doi.org/10.1016/j.ijleo.2010.11.029</u>

- [28] Chattopadhyay, T. (2012) Terahertz Optical Asymmetric Demultiplexer (TOAD) Based Half-Adder and Using It to Design All-Optical Flip-Flop. *Optik*, **123**, 1961-1964. <u>http://dx.doi.org/10.1016/j.ijleo.2011.11.012</u>

- [29] Wang, B.C., Baby, V., Tong, W., Xu, L., Friedman, M., Runser, R.J., Glesk, I. and Prucnal, P.R. (2002) A Novel Fast Optical Switch Based on Two Cascaded Terahertz Optical Asymmetric Demultiplexers (TOAD). *Optics Express*, 10, 15-23. <u>http://dx.doi.org/10.1364/OE.10.000015</u>

- [30] Minh, H.L., Ghassemlooy, Z., Ng, W.P. and Ngah, R. (2004) Terahertz Optical Asymmetric Demultiplexer Switch with a Symmetrical Switching Window. *Proceedings of the London Communication Symposium*, University College, London, 89-92.

- [31] Barman, A.D., Fresi, F., Sengupta, I.I., Potì, L. and Bogoni, A. (2009) Theoretical and Experimental Investigation of Inter-Channel Crosstalk Mitigation by Assist Light in a TOAD De-Multiplexer. *Proceedings of the International Conference on Computers and Devices for Communication*, (IEEE CODEC'09), Kolkata, 14-16 December 2009, 1-4.

- [32] Lu, D., Jia, N., Zhong, K.P., Chen, M., Li, T.J. and Jian, S.S. (2009) Experimental and Theory Study the System Performance of TOAD Using for Demultiplexing in 160gb/S OTDM Transmission System. *Proceedings of the Communications and Photonics Conference and Exhibition (ACP)*, Asia, Shanghai, 2-6 November 2009, 1-7.

- [33] Zoiros, K.E., Kalaitzi, A. and Koukourlis, C.S. (2010) Study on the Cascadability of a SOA-Assisted Sagnac Switch Pair. *Optik*, **121**, 1180-1193. <u>http://dx.doi.org/10.1016/j.ijleo.2009.01.001</u>