# Simulation of Seven and Nine Level CHBMLI with Elliptical Phase Disposition PWM Technique

## Chinmayi<sup>1</sup>, B. G. Shivaleelavathi<sup>2</sup>, Veeramma Yatnalli<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Jyothy Institute of Technology, Bengaluru, Visvesvaraya Technological University, Belagavi, Karnataka, India

<sup>2</sup>Department of Electronics and Communication Engineering, JSS Academy of Technical Education, Bengaluru, Visvesvaraya Technological University, Belagavi, Karnataka, India

Email: shivaleelavathi@gmail.com

How to cite this paper: Chinmayi, Shivaleelavathi, B.G. and Yatnalli, V. (2020) Simulation of Seven and Nine Level CHBMLI with Elliptical Phase Disposition PWM Technique. *Journal of Power and Energy Engineering*, **8**, 49-63.

https://doi.org/10.4236/jpee.2020.83004

**Received:** February 27, 2020 **Accepted:** March 28, 2020 **Published:** March 31, 2020

Copyright © 2020 by author(s) and Scientific Research Publishing Inc. This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

#### Abstract

Electric vehicles are in demand in recent days due to depleting conventional energy resources. Electric vehicles which are environmental friendly are set to increase on road in coming days. The Electric vehicles which consist of electric drive systems are made up of electric motors, inverters and batteries. There is a need to increase their output quality while decreasing their size and cost. The multilevel inverter plays a vital role in improving the quality of the output voltage of the inverter. This paper presents the implementation of Elliptical Phase Disposition Pulse Width Modulation (EPD PWM) technique for higher level of Cascaded H-Bridge Multi Level Inverter (CHBMLI). The performance of 5, 7 and 9-level CHBMLI with proposed EPD PWM scheme is analyzed for three-phase RL-load. The simulation results prove that the voltage %THD reduces from 28.09 to 12.85 to 9.69 and current %THD reduces from 25.58 to 10.22 to 9.42 as the number of inverter output level increases from 5-7-9 level respectively. The simulation is carried out on MATLAB/ SIMULINK platform and the results were compared with conventional method to validate the proposed scheme. The simulation results prove that the novel EPD-PWM technique can be used to effectively control the CBHMLI.

#### **Keywords**

Electric Vehicles (EVs), MATLAB/Simulink, %THD, EPD PWM Technique, Multi Level Inverter (MLI), CHBMLI

# **1. Introduction**

Inverters convert DC power from batteries to alternating current to accelerate or

decelerate the vehicle speed and to control the motor speed and torque. The PWM technique is used to change the output frequency of the inverters, which changes required speed of the drive. The inverters required so are to be highly efficient and reliable [1]. Inverters are expensive component of EV power conversion system and also it is the critical factor in terms of overall system reliability and operation [1]. The AC output produced by the inverter can have square wave, quasi sine wave, modified sine or pure sine wave waveforms. The pure sine wave inverters are preferred as it has high efficiency and best power quality compared to remaining output types. The Total Harmonic Distortion (THD) of the inverter output is governed by the shape of the distorted wave. The poor power quality and the presence of %THD in square, modified sine and quasi sine wave definitely affects the performance of the load connected to the inverter output. Hence, the pure sine wave inverters are preferred for enhancing the quality of the output power so that life of the loads is increased.

To achieve the pure sine wave outputs at the inverter, Multi Level Inverters (MLI) are used. The MLI converts power from DC to AC in multilevel voltage steps to obtain sinusoidal voltage with lower switching losses, improved electromagnetic compatibility and higher dv/dt capability [2] [3]. The different topologies of MLI that can generate a stepped voltage waveform and that are suitable for different applications are Diode Clamped MLI, Capacitor Clamped or Flying Capacitor (FC) MLI, Neutral Point Clamped (NPC) MLI, Cascaded H-bridge (CHBMLI), etc. [4] [5] [6] [7].

The CHBMLI very agreeable for high power medium voltage drives and even for utility applications, for regenerative type motor drive, Hybrid electric vehicles, Vehicles which are based on Fuel cells, main traction drives used in electrical vehicles. As the topology requires isolated DC sources, CHBMLI are perfect for linking PV power generation with an AC grid such as in Fuel cells or PV cells, they are used in static Var generators [8].

Research shows that not a single PWM method is the best suited for all applications. There are numerous PWM Techniques developed in the field with advances in solid-state power electronics devices and microcontrollers. For above reasons, the PWM techniques are considered for intensive research subject since 1970's [9]. To minimize harmonics and switching losses in inverters, particularly in three-phase systems, PWM strategy has an important role. The main objective of modulation technique is to achieve a variable output with a supreme fundamental component and least harmonics.

The "MCPWM" methods are widely used in majority of the MLI applications [10] [11]. Sinusoidal PWM (SPWM) is one of the initial modulation signals for multicarrier based PWM. The "SPWM" technique compares a carrier signal and a pure sinusoidal modulation signal. The utilization rate of DC bus voltage for the traditional sinusoidal PWM is only 78.5%. Improvement in the rate of the DC bus voltage utilization has been the focus for research in power electronics [12].

The under-utilization of the DC bus voltage in traditional sinusoidal PWM, headed to the development of "Third Harmonic Injection PWM (THIPWM)", which added a third-order harmonic content into the sinusoidal reference signal resulting in an increase of 15.5% in the utilization rate of the DC bus voltage [12].

Abbas *et al.* [13] present the effect of over-modulation technique on single-stage three-phase grid-connected boost inverter. Performance of THIPWM is compared with over-modulation of SPWM. The THIPWM increases the inverter gain by 15% without distorting the inverter output voltage. The amplitude of modulating sinusoid is increased beyond the input voltage; the capacitor voltage will clip to input voltage. The output voltage increases during the over-modulation, but due to the clipping of the capacitors' voltage, the waveform is distorted.

Space-Vector PWM (SVPWM), one more method of enhancing the output voltage. When compared with the SPWM technique, the SVPWM technique generates less harmonics distortion and utilizes the DC bus voltage more efficiently. The "SVPWM" technique has the maximum peak fundamental magnitude of nearly 90.6% of the inverter capacity. The rise in the maximum voltage compared with conventional SPWM is 15.5% [14] [15].

Zulkifile *et al.* [16] compare SPWM, THIPWM and SVPWM for three-phase Voltage Source Inverters. The performance comparison is evaluated in terms of inverter output voltage, modulation index and switching frequency. The simulation outcomes conclude that the SPWM technique is not proficient in over modulation region and not suitable for high frequency applications. THD remains constant with the variation in input voltage for SPWM and THIPWM.

Phuong Hue Tran *et al.* [17] assessed 3 different PWM techniques "SPWM", "THIPWM" and "SVPWM" in the linear and over modulation mode and concludes from simulation results of all three PWM techniques that "SVPWM" and "THIPWM" have a greater performance compared to SPWM. SVPWM technique is intensively studied in the over-modulation region owing to its performance benefits when compared to SPWM and THIPWM, as it has higher modulation index, lower switching losses, less THD. 5% increase in ma. But SVPWM can only be applied to three-phase converters [16].

The "SPWM" technique is the easiest modulation technique to understand and to implement in software and hardware. However, this technique is incapable to fully utilize the DC bus voltage and this shortcoming led to the development of "THIPWM" and "SVPWM". In "THIPWM" technique a third-order harmonic content is added to a sinusoidal modulating signal thereby increasing the utilization rate of DC bus voltage by 15.5%. The implementation of the "SVPWM" is comparatively difficult as it requires complex mathematical operations. In under-modulation region, this algorithm provides 15.5% improved output voltages when compared to the traditional "SPWM" technique.

The present research paper proposes a novel Elliptical modulating for MCPWM technique to improve the DC bus voltage utilization. The increase in the DC bus utilization is achieved without operating PWM in over modulation region and

without injecting "third harmonic". The proposed EMC PWM technique can be easily extended to any number of output level of inverter without any complex mathematical operations involved.

This paper presents simulation of Elliptical Phase Disposition PWM (EPD-PWM) technique to control 5, 7 and 9-level inverter connected with RL-Load. The simulation results show that, as the number of levels at the output increases, the output voltage becomes smoother and also reduced harmonic content when compared to PD PWM technique [18]. The subsequent sections present the 5-level, 7-level and 9-level CHBMLI topologies with RL-Load, Simulation results Discussion and Conclusion.

# 2. Five-Level CHBMLI with RL-Load

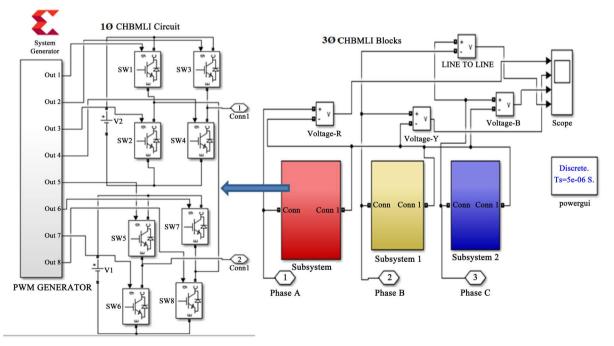

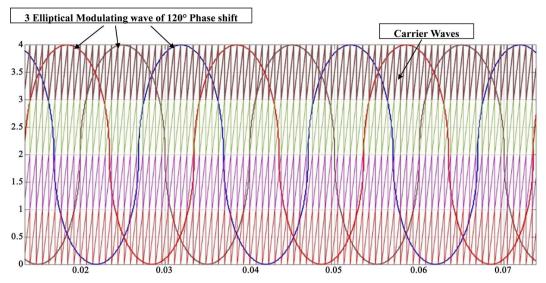

**Figure 1** shows the H-bridge arrangement for 5-level output [19]. An m-level CHBMLI comprises of 2 (m - 1) power semi-conductor switches, (m - 1)/2 H-Bridge cells which are fed with separate DC sources. These H-Bridges are connected in series to obtain the required m-level output. This MLI can generate nearly sinusoidal voltage waveform with one time switching per cycle of switches resulting in reduced switching losses. **Figure 2** shows the use of elliptical modulating with the 4 carrier waves used for generating the PWM for the eight switches of the five-level CHBMLI.

## 3. Seven-Level CHBMLI with RL-Load

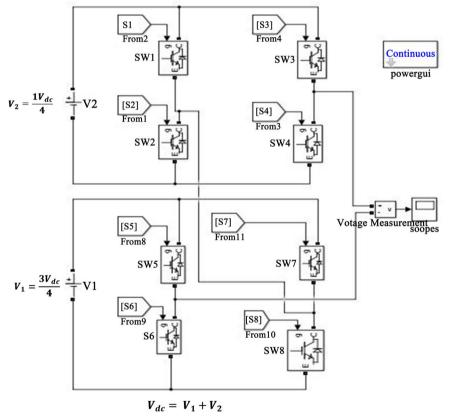

To achieve seven-level output in single-phase CHBMLI, the asymmetrical [20] sources of values  $V1 = 3/4 V_{dc}$  and  $V2 = 1/4 V_{dc}$  are used, where  $V_{dc} = 325 V$  to achieve r.m.s output voltage of 230 V at the inverter of Figure 3 [21]. The

Figure 1. Simulation model of Three-phase 5-level CHBMLI topology for 5-level output.

**Figure 2.** Comparison of carrier waves with three elliptical modulating waves of 120° phase shift for generating switching pulses.

Figure 3. Single Phase 7-level CHBMLI with Asymmetrical DC sources.

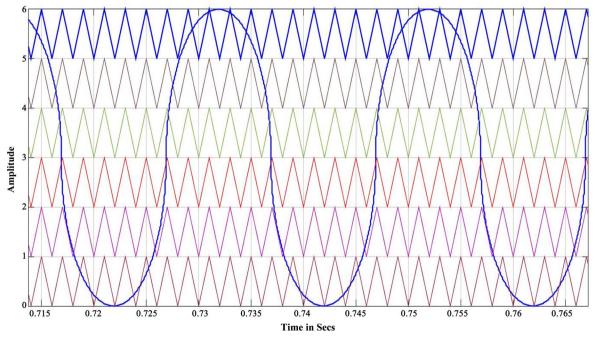

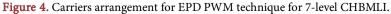

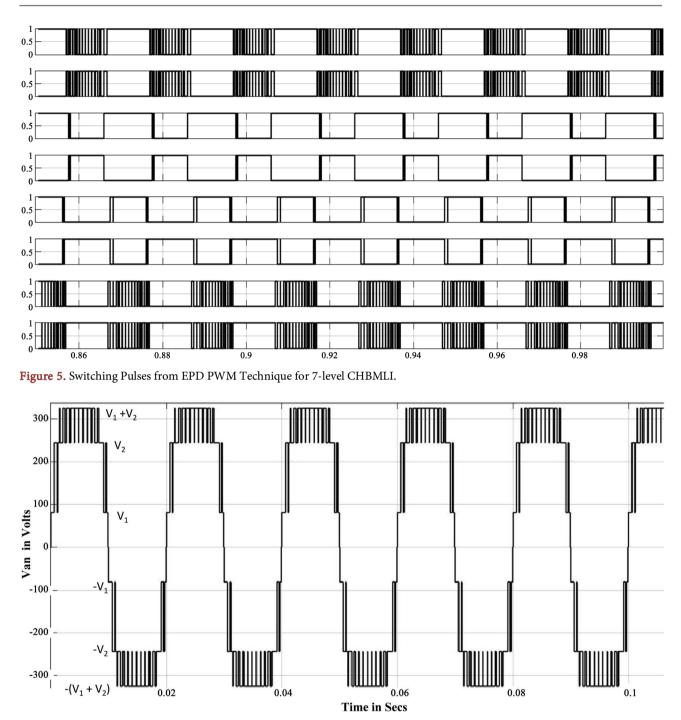

switching sequence for switches to attain seven-level at the output of the inverter is given in **Table 1** [22]. To generate the required switching pulses the EPD PWM technique is used as shown in **Figure 4**, where in six carrier waves are compared with elliptical modulating wave and the switching pulses generated are shown in **Figure 5**. The carrier frequency of 1350 Hz and elliptical modulating wave of fundamental frequency 50 Hz are set in the simulation.

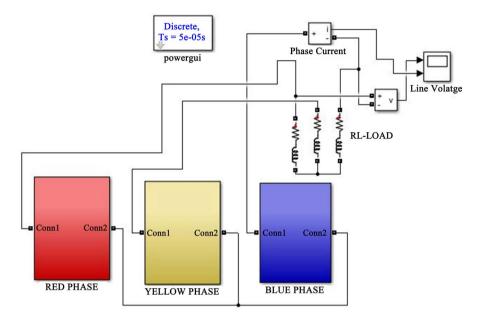

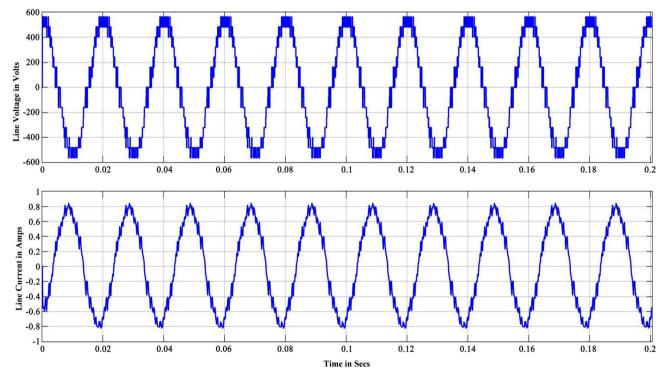

The output voltage waveform obtained for seven-level CHBMLI at no-load is shown in **Figure 6**. The waveform indicates the seven-level marked with DC voltage level of {0, V1, V2, (V1 + V2), -V1, -V2, -(V1 + V2)}. To generate the PWM pulses for three-phase CHBMLI, elliptical modulating waves of 120° phase difference are compared with 6 carrier waves. The generated switching pulses were applied to respective ABC phases to obtain three-phase output. When a RL-Load of 400  $\Omega$  and 40 mH is connected across the three-phase CHBMLI the simulation circuit is shown in **Figure 7**. The Output voltage waveform and current waveform at modulation index set to 0.8 measured from the scope is as shown in **Figure 8**.

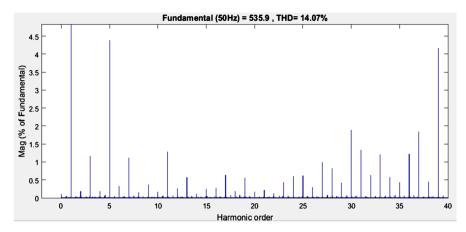

The output voltage is having an r.m.s value of 380 V with load current being 0.54 A. The corresponding FFT spectrum of voltage is shown in **Figure 9** reads

Table 1. The switching states of 7-level CHBMLI.

| Switches when turn ON | Voltage level V <sub>dc</sub> |  |

|-----------------------|-------------------------------|--|

| \$1, \$4, \$5, \$8    |                               |  |

| S5, S8                | 3V <sub>dc</sub> /4           |  |

| S1, S4                | $V_{dc}/4$                    |  |

| No switches are ON    | 0                             |  |

| \$3, \$2              | $-V_{dc}/4$                   |  |

| S5, S6                | -3V <sub>dc</sub> /4          |  |

| \$3, \$2, \$7, \$6    | $-V_{dc}$                     |  |

**Figure 6.** No-load output voltage of 7-Level CHBMLI with EPD PWM Technique at  $m_a = 1$ .

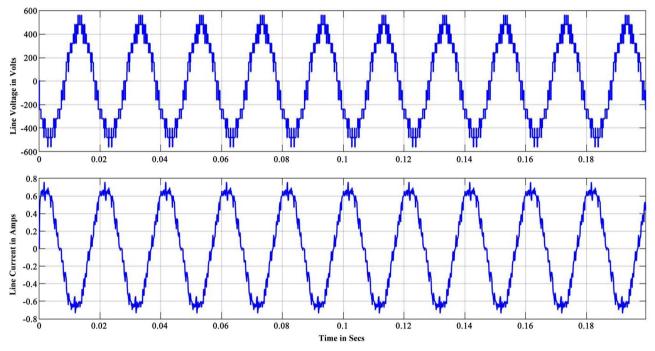

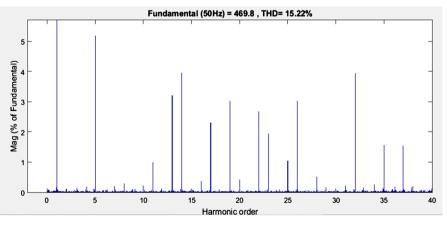

14.07%. For the same simulation conditions, the output voltage waveform and current waveform and the corresponding FFT spectrum for PD PWM technique are shown in **Figure 10** and **Figure 11** respectively. The output obtained from the two PWM methods indicates that the proposed method has resulted in increased output voltage and current with reduction in %THD.

As the number of level in the output increases, output waveform will be very near to sine wave, hence the waveform becomes smoother. The harmonic content also reduces and quality of the waveform also improves. The same features can be noticed when the proposed EPD PWM technique is applied to 7-level CHBMLI. The results obtained from three-phase 5-level CHBMLI and 7-level CHBMLI for the same simulation conditions are compared in **Table 3**. The comparison is made for line voltage, line current and %THD for different modulation indices at fundamental frequency of 50 Hz. The results clearly show that

Figure 7. Three-Phase 7-level CHBMLI with RL-load.

**Figure 8.** Output line Voltage and Current Waveform of three-phase 7-level CHBMLI with EPD PWM Technique with RL-Load at  $m_a = 0.8$ .

**Figure 9.** FFT spectrum of output line voltage of EPD PWM technique with  $m_a = 0.8$ .

**Figure 10.** Output line Voltage and Current Waveform of three-phase 7-level CHBMLI with PD PWM Technique with RL-Load at  $m_a = 0.8$ .

DOI: 10.4236/jpee.2020.83004

there is an increase in the output voltage of 7-level CHBMLI.

The comparison is made for line voltage, line current and %THD for different modulation indices at fundamental frequency of 50 Hz. The results clearly show that there is an increase in the output voltage of 7-level CHBMLI.

At  $m_a = 1$ , the output of 7-level CHBMLI produces a line voltage of 454 V when compared to 5-level CHBMLI which is producing 452.5 V. At the same time the harmonic spectrum has also been reduced at all modulation indices in the 7-level CHBMLI. Even the r.m.s current is increased in 7-level CHBMLI. There is remarkable suppression of current harmonics in the 7-level compared to 5-level inverters, which results in reducing the output filter component size.

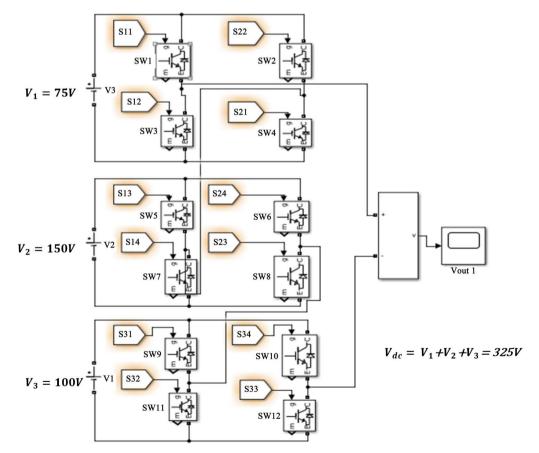

#### 4. Nine-Level Single-Phase CHBMLI

**Figure 12** shows the 9-level CHBMLI with three H-Bridges connected to separate DC sources having values 75 V, 150 V and 100 V, so that the total input voltage is equal to 325 V. The Elliptical Phase Disposition PWM technique is used to control the output voltage with a switching frequency of 1350 Hz. The switching table to generate the 9-level output voltage is listed in **Table 2** and the output no-load voltage in **Figure 13**.

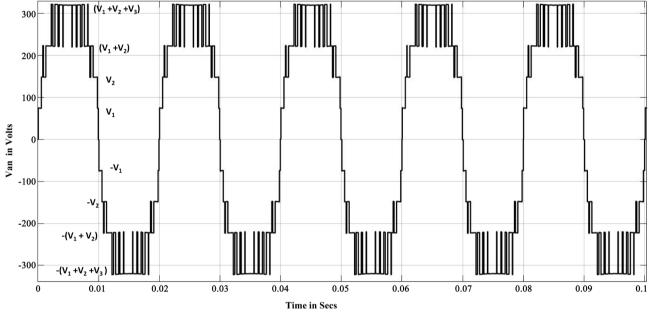

The output voltage waveform obtained for 9-level CHBMLI at no-load is shown in Figure 13. The waveform indicates the seven-level marked with DC

Figure 12. Nine-level single-phase CHBMLI circuit with No-load.

| Switches when turn ON        | Voltage level |

|------------------------------|---------------|

| \$1, \$4, \$5,\$8, \$9, \$12 | V1 + V2 + V3  |

| \$1,\$4, \$5, \$8, \$9, \$10 | V1 + V2       |

| S2,S4, S5, S8, S9, S10       | V2            |

| S1, S4, S7, S8, S9, S10      | V1            |

| No switches are ON           | 0             |

| S2, S3, S7, S8, S9, S10      | -V1           |

| S2, S4, S7, S6, S9, S10      | -V2           |

| S2, S3, S7, S6, S9, S10      | V1 + V2       |

| S2, S3, S7, S6, S11, S10     | V1 + V2 + V3  |

Table 2. Switching table to generate 9-level output voltage.

Figure 13. Output phase voltage of 9-level CHBMLI with no-Load.

voltage level of {0, V1, V2, (V1 + V2), (V1 + V2 + V3), -V1, -V2, -(V1 + V2), -(V1 + V2 + V3)}. To generate the PWM pulses for three-phase CHBMLI, elliptical modulating waves of 120° phase difference are compared with 8 carrier waves. The generated switching pulses were applied to respective ABC phases to obtain three-phase output. When a RL-Load of 400  $\Omega$  and 40 mH is connected across the three-phase CHBMLI.

# **5. Simulation Results Discussion**

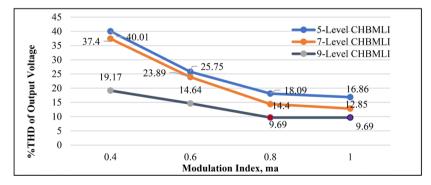

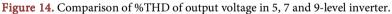

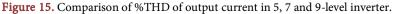

The performance comparison of 5, 7 and 9-level three-phase inverters are listed in **Table 3**. The output at the inverter is maintained to 325 V peak to achieve 230 V r.m.s value and 400 V line voltage. The modulation index is varied from 0.4 to 1 and the output voltage and current are recorded with corresponding %THDs. From the outputs obtained at modulation index 1 of all the three-level inverters shows that there is an increase in the output r.m.s value compare to sinusoidal PWM technique [18] [23] [24]. The output voltage quality has also improved with reduction in the %THD. The comparison chart is shown in Figure 14 for output voltage harmonic contents and Figure 15 for output current harmonics

**Table 3.** Performance comparison of EPD PWM Technique fed Three-phase 5-Level, 7-level and 9-level CHBMLI with RL-Load.

| Output Level | M <sub>a</sub> | V <sub>rms</sub> | %THD <sub>v</sub> | $I_{line}$ | %THD <sub>I</sub> |

|--------------|----------------|------------------|-------------------|------------|-------------------|

| 5-level      | 1              | 452.5            | 16.86             | 0.61       | 20.88             |

|              | 0.8            | 362.2            | 18.09             | 0.514      | 25.85             |

|              | 0.6            | 271.7            | 25.75             | 0.385      | 25.18             |

|              | 0.4            | 181.1            | 40.01             | 0.258      | 40.4              |

| (            | 1              | 454              | 12.85             | 0.65       | 10.36             |

|              | 0.8            | 380.1            | 14.4              | 0.54       | 10.22             |

|              | 0.6            | 273.2            | 23.89             | 0.39       | 15.16             |

|              | 0.4            | 245.5            | 37.4              | 0.2        | 21.8              |

| 9-Level      | 1              | 442.1            | 9.69              | 0.632      | 8.88              |

|              | 0.8            | 337.6            | 9.69              | 0.483      | 9.42              |

|              | 0.6            | 249              | 14.64             | 0.357      | 10.38             |

|              | 0.4            | 166.7            | 19.17             | 0.238      | 13.05             |

proves that, as the number of output level increases the harmonics reduces achieving improved performance of the inverter which reduces the losses thereby increasing the efficiency of the inverter system in power conversion.

#### 6. Conclusion

The proposed novel Elliptical Phase Disposition PWM (EPDPWM) technique is applied to three-phase 5, 7 and 9-level CHBMLI and the performance are investigated. The results of line voltage and %THD for both voltage and current are noted for different modulation indices. The proposed elliptical wave produces enhanced output line voltage and the %THD reduces and is less when compared to conventional Sine PWM. Simulation results illustrate the performance and effectiveness of the proposed EPD-PWM Technique in generating a high quality five, seven and nine-level multilevel inverter output voltage waveform. The proposed EPD PWM technique can be easily extended to any output level of the inverter, with less complexity involved in the implementation of control strategy and PWM generation. Also, it works very efficiently improving DC bus utilization 15% compared to traditional MCPWM technique. This increase in the output is obtained without over-modulation and without third harmonic injection to modulating wave.

# **Conflicts of Interest**

The authors declare no conflicts of interest regarding the publication of this paper.

#### References

- Kimura, T., Saitou, R., *et al.* (2014) High-Power-Density Inverter Technology for Hybrid and Electric Vehicle Applications. *Hitachi Review*, 63, 41-47.

- [2] Chinnaiyan, V.K., Jerome, J. and Karpagam, J. (2013) An Experimental Investigation on a Multilevel Inverter for Solar Energy Applications. *Electrical Power and Energy Systems*, 47, 157-167. <u>https://doi.org/10.1016/j.ijepes.2012.10.025</u>

- [3] Panagis, P., Stergiopoulos, F., Marabeas, P. and Manias, S. (2008) Comparison of State of the Art Multilevel Inverters. *IEEE Power Electronics Specialists Conference*, Rhodes, 15-19 June 2008, 4296-4401. https://doi.org/10.1109/PESC.2008.4592633

- [4] Mittal, N., Singh, B., Singh, S.P., Dixit, R. and Kumar, D. (2012) Multilevel Inverters: A Literature Survey on Topologies and Control Strategies. 2nd IEEE International Conference on Power, Control and Embedded Systems, Allahabad, 17-19 December 2012, 1-11. https://doi.org/10.1109/ICPCES.2012.6508041

- [5] Fria, A., El Bachtiria, R. and El Ghzizala, A. (2013) A Comparative Study of Three Topologies of Three-Phase (5L) Inverter for a PV System. *Energy Procedia*, 42, 436-445. <u>https://doi.org/10.1016/j.egypro.2013.11.044</u>

- [6] Zeng, Z., Yang, H., Zhao, R.X. and Cheng, C. (2016) Topologies and Control Strategies of Multi-Functional Grid-Connected Inverters for Power Quality Enhancement: A Comprehensive Review. *Renewable and Sustainable Energy Reviews*, 24, 223-270. <u>https://doi.org/10.1016/j.rser.2013.03.033</u>

- [7] Khalili, T., Raihani, A., Ouajji, H., Bouattane, O. and Amri, F. (2015) Efficient

Choice of a Multilevel Inverter for Integration on a Hybrid Wind-Solar Power Station. *Journal of Power and Energy Engineering*, **29**, 44-58. <u>https://doi.org/10.4236/jpee.2015.39004</u>

- [8] Daher, S., Schmid, J. and Antunes, F.L.M. (2008) Multilevel Inverter Topologies for Stand-Alone PV Systems. *IEEE Transactions on Industrial Electronics*, 55, 2703-2712. https://doi.org/10.1109/TIE.2008.922601

- [9] Naumanen, V. (2010) Multilevel Converter Modulation: Implementation and Analysis. Thesis for the Degree of Doctor of Science (Technology), Lappeenranta University of Technology, Lappeenranta.

- [10] Shalchi, R. and Hosseini, S.H. (2015) A New Multilevel Inverter Structure for High-Power Applications Using Multicarrier PWM Switching Strategy. *International Journal of Power Electronics and Drive Systems*, 6, 318-325. <u>https://doi.org/10.11591/ijpeds.v6.i2.pp318-325</u>

- [11] Rao, K., Srinivas, R. and Suresh Kumar, M.V. (2014) Design and Analysis of Various Inverters Using Different PWM Techniques. *The International Journal of Engineering and Science*, 41-51.

- [12] Quan, H.L., et al. (2011) Study of a Novel Over-Modulation Technique Based on Space-Vector PWM. IEEE Computer Distributed Control and Intelligent Environmental Monitoring, Changsha, 19-20 February 2011, 295-298. https://doi.org/10.1109/CDCIEM.2011.187

- [13] Abbas Elserougi, A., Abdel-Khalik, A.S., Massoud, A. and Ahmed, S. (2013) Studying the Effect of Over-Modulation on the Output Voltage of Three-Phase Single-Stage Grid-Connected Boost Inverter. *Alexandria Engineering Journal*, **52**, 347-358. <u>https://doi.org/10.1016/j.aej.2013.05.006</u>

- [14] Leedy, A.W. and Nelms, R.M. (2006) Harmonic Analysis of a Space Vector PWM Inverter Using the Method of Multiple Pulses. *IEEE Transactions on Industrial Electronics*, 4, 1182-1187. <u>https://doi.org/10.1109/ISIE.2006.295805</u>

- [15] Zhou, K. and Wang, D. (2002) Relationship between Space-Vector Modulation and Three-Phase Carrier-Based PWM: A Comprehensive Analysis. *IEEE Transactions* on Industrial Electronics, 49, 186-196. <u>https://doi.org/10.1109/41.982262</u>

- [16] Ibrahim, Z.B., Hossain, M.L., Bugis, I.B., Mahadi, N.M.N. and Hasim, A.S.A. (2014) Simulation Investigation of SPWM, THIPWM and SVPWM Techniques for Three Phase Voltage Source Inverter. *International Journal of Power Electronics and Drive System*, 4, 223-232. <u>https://doi.org/10.11591/ijpeds.v4i2.5833</u>

- [17] Tran, P.H. (2012) MATLAB/Simulink Implementation and Analysis of Three Pulse-Width-Modulation (PWM) Techniques. Thesis of Master of Science in Electrical Engineering Boise State University.

- [18] Jayapalan, G. and Edward, B. (2018) Design and Implementation of 15-Level Asymmetric Cascaded H Bridge Multilevel Inverter. *Journal of Electrical Engineering*, 17, 396-404. <u>http://www.jee.ro</u>

- [19] Rashid, M.H. (2004) Power Electronics: Circuits, Devices and Applications. Third Edition, Pearson Publication, London, 411-422.

- [20] Srikanth, C. and Shivaleelavathi, B.G. (2017) A Novel Implementation of Digital Control Strategy for Multilevel Inverters Using FPGA Wavect Controller. *IEEE* 18th Workshop on Control and Modeling for Power Electronics, Stanford, 9-12 July 2017, 1-6. <u>https://doi.org/10.1109/COMPEL.2017.8013338</u>

- [21] Kumar, M.S. and Ramani, K. (2014) Comparative Review of Modulation Techniques for Harmonic Minimization in Multilevel Inverter, World Academy of Science, Engineering and Technology. *International Journal of Electrical, Comput-*

er, Energetic, Electronic and Communication Engineering, 8, 1938-1945.

- [22] Singh, A., Jain, M. and Singh, S. (2015) Analysis of THD and Output Voltage for Seven Level Asymmetrical Cascaded H-Bridge Multilevel Inverter Using LSCPWM Technique. *International Journal of Computer Applications*, **112**, 1-6.

- [23] Srikanth, C. and Shivaleelavathi, B.G. (2018) Digital Control of Three-Phase Cascaded Multilevel Inverter Using FPGA Wavect Tool. *International Journal of Power Electronics and Drive System*, 9, 189-197. https://doi.org/10.11591/ijpeds.v9.i1.pp189-197

- [24] Srikanth, C. and Shivaleelavathi, B.G. (2017) V/F Control of Three-Phase Induction Motor Using 7-Level Cascaded H-Bridge Inverter. *International Conference on Signal, Image Processing Communication and Automation*, Bengaluru, 6-7 July 2017, 257-262.