Published Online March 2016 in SciRes. <a href="http://www.scirp.org/journal/ijmnta">http://dx.doi.org/10.4236/ijmnta.2016.51007</a>

# Design of 2-to-4 All-Optical Decoder with the Help of Terahertz Optical Asymmetric Demultiplexer

#### Arunava Bhattacharyya<sup>1</sup>, Dilip Kumar Gayen<sup>1</sup>, Tanay Chattopadhyay<sup>2</sup>

- <sup>1</sup>Department of Information Technology and Computer Science, College of Engineering & Management, Kolaghat, India

- <sup>2</sup>Mechanical Operation (Stage-II), Kolaghat Thermal Power Station, WBPDCL, West Bengal, India Email: dilipgayen@yahoo.com

Received 10 December 2015; accepted 7 March 2016; published 10 March 2016

Copyright © 2016 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY). <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>

Open Access

#### **Abstract**

An all-optical 2-to-4 decoder unit with the assist of terahertz optical asymmetric demultiplexer (TOAD) is presented. The all-optical 2-to-4 decoder with a set of all-optical switches is designed which can be used to achieve a high-speed central processor unit using optical hardware. The unique output lines can be used for all-optical header processing. We attempt to develop an integrated all-optical circuit which can perform decoding of signal. This scheme is very simple and flexible for performing different logic operation and to design advanced complex logic. Simulated results are confirming the described methods.

## **Keywords**

Terahertz Optical Asymmetric Demultiplexer, Semiconductor Optical Amplifier, All-Optical Decoder

#### 1. Introduction

By the advent of optical networks and optical communication systems need for all-optical circuits and devices has been started. Currently communication networks aim to reach very bit rates and ultrafast data transfer rates with terabit per second bit rates. In order to achieve such a high bit rate, we should have a complete optical network without any electronics to optical conversion. In such a network, all communication steps such as sending, receiving and data processing should be performed totally in optical domain. A decoder is important for header processing in typical core router/demultiplexer for addressing output port. There are many research areas which

How to cite this paper: Bhattacharyya, A., Gayen, D.K. and Chattopadhyay, T. (2016) Design of 2-to-4 All-Optical Decoder with the Help of Terahertz Optical Asymmetric Demultiplexer. *International Journal of Modern Nonlinear Theory and Application*, **5**, 67-72. <a href="http://dx.doi.org/10.4236/ijmnta.2016.51007">http://dx.doi.org/10.4236/ijmnta.2016.51007</a>

have been proposed using various all-optical switching and all-optical logic operation, such as all-optical pack-et-switching [1], all-optical demultiplexing [2] semiconductor optical amplifier (SOA) [3]-[5], TOAD based interferometer device [6]-[9], cascaded microring resonators [10], and all-optical code conversion [11]-[13]. Among the different proposed schemes, the terahertz optical asymmetric demultiplexer (TOAD)/semiconductor optical amplifier (SOA)-assisted Sagnac gate effectively combines fast switching time and a reasonable noise figure, with the ease of integration and overall practicality that enables it to compete favorably with other similar optical time division multiplexing devices. TOAD is characterized by the attractive features of low power consumption, fast switching time, low latency, high repetition rate, jitter tolerance, noise and thermal stability, compactness and high nonlinear properties, which allow their competent utilization in a real ultra-high speed optical communications environment. TOAD has the potential of being integrated, which can be frequently and consistently manufactured and massively produced so that they can be of viable value.

In this paper we propose and describe the TOAD based switch to design 2-to-4 line decoder in all-optical domain. It can convert binary information from n input line to a maximum of  $2^n$  unique output line.

# 2. Operation of TOAD Based Switch

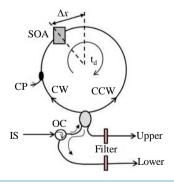

The basic design of TOAD based switch is shown in **Figure 1** [6]. Here a semiconductor optical amplifier (SOA) is placed asymmetrically in a loop. The output power at upper and lower can be expressed as [7]-[9] [11]-[13]

$$P_{\text{Upper}}(t) = \frac{P_{IS}(t)}{4} \times \left\{ G_{cw}(t) + G_{ccw}(t) - 2\sqrt{G_{cw}(t)} \times G_{ccw}(t) \times G_{ccw}(t) \right\}$$

(1)

$$P_{\text{Lower}}(t) = \frac{P_{IS}(t)}{4} \times \left\{ G_{cw}(t) + G_{ccw}(t) + 2\sqrt{G_{cw}(t)} \times G_{ccw}(t) \times G_{ccw}(t) \right\}$$

(2)

where,  $G_{cw}(t)$ ,  $G_{ccw}(t)$  is the power gain.

The time-dependent phase difference between clockwise (CW) and counter clockwise (CCW) pulses [7]-[9] is

$$\Delta \varphi = -\frac{\alpha}{2} \ln \left[ \frac{G_{cw}(t)}{G_{ccw}(t)} \right]$$

(3)

with  $\alpha$  being the line-width enhancement factor. In the absence of a control signal, data signal (incoming signal) enters the fiber loop, pass through the SOA at different times as they counter-propagate around the loop and experience the same unsaturated small amplifier gain  $G_{ss}$  and recombine at the input coupler *i.e.*  $G_{ccw} \approx G_{cw}$ . Then,  $\Delta \varphi \approx 0$  and expression for  $P_{up} \approx 0$  and  $P_{LOW}(t) = P_{IS}(t) \cdot G_{ss}$ . It shows that data is reflected back toward the source. When a control pulse is injected into the loop (CP = on), it saturates the SOA at time  $t_s$  and changes its index of refraction. The gain of the SOA decreases rapidly as [11]-[13]:

$$G(t) = \frac{1}{1 - \left(1 - \frac{1}{G_{SS}}\right) \exp\left(-\frac{E_{cp}(t)}{E_{sat}}\right)}$$

(4)

**Figure 1.** A TOAD based optical switch with single control pulse (CP), where SOA: semiconductor optical amplifier, CW: clockwise pulse, CCW: counterclockwise pulse,  $t_d$ : pulse round trip time,  $\Delta x$ : asymmetric distance, IS: incoming signal and OC: optical circulator.

where,  $E_{sat}$  is the saturation energy of the SOA,  $G_0$  is the unsaturated single-pass amplifier gain. Here we consider Gaussian pulse  $P_{cp}(t) = \frac{E_{cp}}{\sigma\sqrt{\pi}} \exp\left(-\frac{t^2}{\sigma^2}\right)$  as control signal.  $E_{cp}$  is the control pulse energy.  $\sigma$  is related to full

width at half maximum (FWHM) by  $T_{FWHM} \cong 1.665\sigma$ .

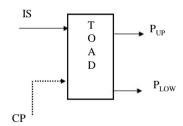

Therefore when they recombine at the input coupler, then  $\Delta \varphi \approx -\pi$  (obtained from Equations (3) and (4)) and the data will exit from the upper port *i.e.*  $P_{UP}(t) \neq 0$  and  $P_{LOW}(t) \approx 0$ , the corresponding values can be obtained from the equations (1) and (2), respectively. The energy of the control pulse is ten times greater than that of the incoming pulse. A filter may be used at the output of TOAD based switch to reject the control and pass the incoming pulse. The schematic diagram of TOAD based switch is shown in **Figure 2**.

## 3. Principle and Design of All-Optical 2-to-4 Decoder

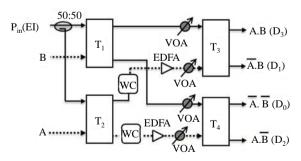

A decoder is a combinational circuit which changes binary information from n inputs to maximum of  $2^n$  unique outputs. The only inputs in decoders are the control bits. In digital electronics, a decoder can capture the shape of a many inputs and outputs logic circuit that converts coded inputs into its coded outputs, where the input and output codes are different e.g. n to  $2^n$ . A 2-to-4 decoder operates according to the truth **Table 1** with enable input (EI). This EI is used for activate (EI = 1) or deactivate (EI = 0) the decoder. Decoding is essential in applications such as memory address, decoding data, multiplexing and 7 segment displays. A block diagram of 2-to-4 decoder (2 input lines and 4 output lines) with enable input (EI) is shown in **Figure 3**.

To implement the optical 2-to-4 decoder, we use TOAD-based optical switches, namely  $s_1$  to  $s_4$  as shown in **Figure 3**. Parallel binary numbers are used as inputs to a decoder and that are used to sense the presence of particular binary information at the input. The output specifies absence or presence of particular number at the decoder input. Here upper and lower ports of  $T_1$  are fed to  $T_3$  and  $T_4$  as incoming signal and both output ports of  $T_2$  are considered as control signals of  $T_3$  and  $T_4$  respectively. In a TOAD based switch the incoming signal is of wavelength  $\lambda_2$  and the control pulse signal is of wavelength  $\lambda_1$ , where  $\lambda_1 \neq \lambda_2$ . So, when a light of wavelength  $\lambda_2$  from an output port of one TOAD based switch is connected as a control signal to another TOAD based switch, then the wavelength  $\lambda_2$  is required to be converted to wavelength  $\lambda_1$  for the second switch. This is done

Figure 2. The schematic diagram of TOAD based switch.

**Figure 3.** A block diagram of all-optical decoder, where  $P_{in}(EI)$ : Incoming light signal (enable input), A and B: input data signals,  $T_1$ - $T_4$ : TOAD based switches, 50:50: 3 dB coupler, WC: wavelength converter, VOA: variable optical attenuator, EDFA:  $Er^{+3}$  doped fiber amplifier. Solid line indicates optical data signal of wavelength  $\lambda_2$  and dotted line indicates control signal path of wavelength  $\lambda_1$ .

with the help of a wavelength converter (WC). Its size is few micrometers and power consumption is also negligible. Then the optical power is amplified by  $Er^{+3}$  doped fiber amplifier (EDFA) with its gain  $G_{EDFA}$ . Power of the wavelength converted amplified signal can be adjusted by variable optical attenuator (VOA) before fed it to the TOAD as control signal. All the output ports of TOADs  $T_3$  and  $T_4$  are utilized to verify the **Table 1**.

In this circuit, we can remove the extra enable input which is required for activate and deactivate the decoder circuit. Here the incoming single  $P_{in}$  itself uses as an enable input. When  $P_{in}$  is 0 *i.e.*, the incoming signal is absence for the switches  $T_1$  and  $T_2$  and no outputs receive any light as filter block the control signal if any. So when  $P_{in}$  is 1 *i.e.*, the incoming signal is present for the switches  $T_1$  and  $T_2$  hence the circuit becomes active and depending on the values of input A and B, the desired output will be obtained at the any of the output terminal of  $D_0$ ,  $D_1$ ,  $D_2$  and  $D_3$ . The logic level "0" and "1" are indicated as "Absence" and "Presence" of light signals respectively. There are 4 different input combinations for implementing double input binary logic, depending on the state of input variables (A and B) when incoming signal is present.

#### 4. Simulated Results

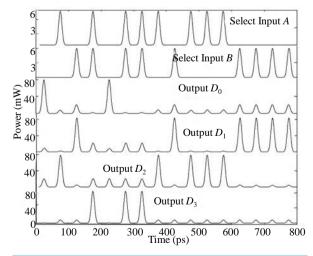

Numerical simulation has been done to confirm the operation of this proposed circuit. The parameters used in this simulation are as follows: saturation energy of the SOA ( $E_{sat}$ ) = 1000 fJ, gain recovery time of the SOA ( $\tau_e$ ) = 50 ps, unsaturated amplifier gain of the SOA ( $G_{ss}$ ) = 30 dB, eccentricity of the loop ( $T_{asym}$ ) = 15 ps, FWHM of the control pulse ( $\sigma$ ) = 3.6 ps, control pulse energy ( $E_{cp}$ ) = 100 fJ, bit period ( $T_c$ ) = 50 ps, and a line-width enhancement factor ( $\alpha$ ) = 6. The simulated input and output waveforms are given in **Figure 4**.

| Enable input | Inputs |   |       | Outputs |       |       |  |

|--------------|--------|---|-------|---------|-------|-------|--|

| EI           | A      | В | $D_0$ | $D_1$   | $D_2$ | $D_3$ |  |

| 0            | 0      | 0 | 0     | 0       | 0     | 0     |  |

| 0            | 0      | 1 | 0     | 0       | 0     | 0     |  |

| 0            | 1      | 0 | 0     | 0       | 0     | 0     |  |

| 0            | 1      | 1 | 0     | 0       | 0     | 0     |  |

| 1            | 0      | 0 | 1     | 0       | 0     | 0     |  |

| 1            | 0      | 1 | 0     | 1       | 0     | 0     |  |

| 1            | 1      | 0 | 0     | 0       | 1     | 0     |  |

| 1            | 1      | 1 | 0     | 0       | 0     | 1     |  |

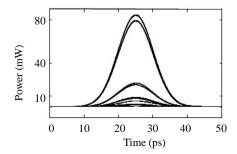

**Figure 4.** A Simulated input and output waveforms, where power (mW) is along the y-axis whereas time is along the x-axis in ps.

In order to assess the performance of the circuit at 20 Gbit/s, we define the contrast ratio (CR) as

$$CR (dB) = 10 \log \left( \frac{P_{\text{mean}}^1}{P_{\text{mean}}^0} \right)$$

(5)

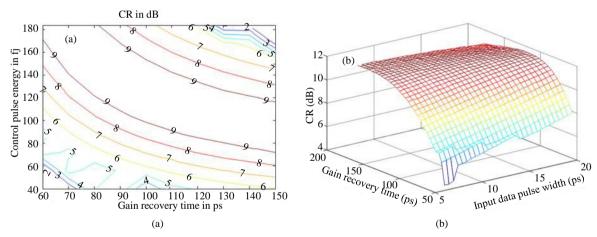

where  $P_{\rm mean}^1$  and  $P_{\rm mean}^0$  is the mean of the peak power of the 1-states and 0-states, respectively. For high performance, it must be as high as possible so that largest fraction of the incoming data signal exits at the target output of the circuit. The operation of the circuit depends on the proper SOA gain saturation and in particular its recovery, it is evident that the carrier lifetime, control pulse energy and input pulse width are important performance parameter. For this reason, the effect on the CR with different control pulse energy and gain recovery time is depicted in **Figure 5**. The common characteristic of all curves in **Figure 5** is that CR increases with increasing control pulse energy and gain recovery time up to a certain value (~100 fJ and ~100 ps) after which CR is decreased. This can be explained physically by considering the SOA dynamic gain response. The saturation energy decreases with decrease of gain recovery time for constant saturation power.

This in turn means that less energy is required in order to saturate the SOA and obtain a large change in the amplification of the counter-propagating pulses. The value of ~100 fJ for control pulse energy, ~100 ps for gain recovery time and pulse width ~12 ps is applied for getting the contrast ratio greater than 9 dB. The lower control pulse energy and small-signal gain values are insufficient for full switching. This occurs because the created phase difference is much less than the required value  $\pi$ , which reduces the contrast ratio. The eye-diagram is the superposition of the outputs for the repetition period of the inputs, *i.e.*, inputs varies from  $0 \rightarrow 0$ ,  $0 \rightarrow 1$ ,  $1 \rightarrow 1$ ,  $1 \rightarrow 0$ , and so on [14]. Figure 6 is called a *pseudo-eye-diagram* [14]. The relative eye opening (O) is defined as  $O = (P_{\min}^1 - P_{\max}^0)/P_{\min}^1$ ,  $P_{\min}^1$  and  $P_{\max}^0$  are the minimum and maximum powers at 1-state and 0-state, respectively, which can be calculated from Figure 6. An eye-diagram with large eyes indicates a clear transmission with a low bit error rate. Here, we get PED (O) = 82.36%, which indicates an excellent response of the circuit to the incoming data at its output terminals.

Figure 5. Variation of CR with (a) control pulse energy and gain recovery time and (b) gain recovery time and pulse width at the outputs.

Figure 6. Simulated output waveforms with pseudo-eye-diagram (PED).

## 5. Conclusion

All-optical decoder is expected to be helpful in optical system nodes because of smartness and flexibility. In this paper, we have proposed and theoretically demonstrated the operations of decoder. By conducting numerical simulation, we have specified the requirements for the input pulse width, gain recovery time and control pulse energy so that the performance metrics of contrast ratio and relative opening of the eye diagram are satisfactory. This model may be expanded for studying more compound all-optical decoder.

#### **Acknowledgements**

The authors are grateful to Technical Education Quality Improvement Programme (TEQIP) phase II by National Project Implementation Unit (Approval No-CEMK/TEQIP-II/R & D/Project/15-16/03) for providing the grant for this work.

#### References

- [1] Teimoori, H., Topomondzo, J.D., Ware, C., Gabet, R. and Erasme, D. (2007) All-Optical Packet-Switching Decoder Design and Demonstration at 10 Gb/s. *IEEE Photonics Technology Letters*, 19, 738-740. http://dx.doi.org/10.1109/LPT.2007.895444

- [2] Olsson, B.E. and Blumenthal, D.J. (2001) All-Optical Demultiplexing Using Fiber Cross-Phase Modulation and Optical Filtering. IEEE Photonics Technology Letters, 13, 875-877. <a href="http://dx.doi.org/10.1109/68.935833">http://dx.doi.org/10.1109/68.935833</a>

- [3] Hun, J., John, Y.M., Byun, Y.T., Lee, S., Woo, D.H. and Kim, S.H. (2002) All-Optical XOR Gate Using Semiconductor Optical Amplifiers without Additional Input Beam. *IEEE Photonics Technology Letters*, 14, 1436-1438. http://dx.doi.org/10.1109/LPT.2002.801841

- [4] Cong, J., Zhang, X. and Huang, D. (2009) A Propose for Two-Input Arbitrary Boolean Logic Gates Using Single Semiconductor Optical Amplifier by Picoseconds Pulse Injection. *Optics Express*, 17, 7725-7730. <a href="http://dx.doi.org/10.1364/OE.17.007725">http://dx.doi.org/10.1364/OE.17.007725</a>

- [5] Kim, S.H., Kim, J.H., Yu, B.G., Byun, Y.T., Jeon, Y.M., Lee, S. and Woo, D.H. (2005) All-Optical NAND Gate Using Cross-Gain Modulation in Semiconductor Optical Amplifiers. *Electronic Letters*, 41, 1027-1028. http://dx.doi.org/10.1049/el:20052320

- [6] Sokoloff, J.P., Prucnal, P.R., Glesk, I. and Kane, M. (1993) A Terahertz Optical Asymmetric Demultiplexer (TOAD). IEEE Photonic Technology Letters, 5, 787-789. <a href="http://dx.doi.org/10.1109/68.229807">http://dx.doi.org/10.1109/68.229807</a>

- [7] Kaur, K. and Bhatia, K.S. (2015) Optical Time Division Multiplexing Using Terahertz Optical Asymmetric Demultiplexer. *Journal of Optical Communications*, **36**, 297-301. <a href="http://dx.doi.org/10.1515/joc-2014-0087">http://dx.doi.org/10.1515/joc-2014-0087</a>

- [8] Li, P., Jiang, L., Zhang, J.G., Zhang, J.Z. and Wang, Y.C. (2015) Low-Complexity Toad-Based All-Optical Sampling Gate with Ultralow Switching Energy and High Linearity. *IEEE Journal of Photonics*, 7, Article ID: 7801108. http://dx.doi.org/10.1109/jphot.2015.2459377

- [9] Gayen, D.K., Chattopadhyay, T., Das, M.K., Roy, J.N. and Pal, R.K. (2011) All-Optical Binary to Gray Code and Gray to Binary Code Conversion Scheme with the Help of Semiconductor Optical Amplifier-Assisted Sagnac Switch. *IET Circuits, Devices & Systems*, 5, 123-131. <a href="http://dx.doi.org/10.1049/iet-cds.2010.0069">http://dx.doi.org/10.1049/iet-cds.2010.0069</a>

- [10] Zhang, L., Ji, R., Jia, L., Yang, L., Zhou, P., Tiam, Y., Chen, P. and Lu, Y. (2010) Demonstration of Directed XOR/XNOR Logic Gates Using Two Cascaded Microring Resonators. *Optics Letters*, 35, 1620-1622. http://dx.doi.org/10.1364/OL.35.001620

- [11] Gayen, D.K., Chattopadhyay, T., Das, M.K., Roy, J.N. and Pal, R.K. (2011) All-Optical Binary to Gray Code and Gray to Binary Code Conversion Scheme with the Help of Semiconductor Optical Amplifier-Assisted Sagnac Switch. *IET Circuits, Devices & Systems*, **5**, 123-131. <a href="http://dx.doi.org/10.1049/iet-cds.2010.0069">http://dx.doi.org/10.1049/iet-cds.2010.0069</a>

- [12] Bhattachryya, A., Gayen, D.K. and Chattopadhyay, T. (2012) All-Optical 4-Bit Binary to Binary Coded Decimal Converter with the Help of Semiconductor Optical Amplifier-Assisted Sagnac Switch. *Optics Communications*, 293, 31-42. http://dx.doi.org/10.1016/j.optcom.2012.11.079

- [13] Gayen, D.K., Bhattacharyya, A., Taraphdar, C., Pal, R.K. and Roy, J.N. (2011) All-Optical Binary Coded Decimal (BCD) Adder with the Help of Terahertz Optical Asymmetric Demultiplexer. *IEEE Computing Science and Engineering*, 13, 50-57. <a href="http://dx.doi.org/10.1109/MCSE.2009.209">http://dx.doi.org/10.1109/MCSE.2009.209</a>

- [14] Gowar, J. (1993) Optical Communication System. 2nd Edition, Prentice Hall of International Limited, UK.