Study of Timing Characteristics of NOT Gate Transistor Level Circuit Implemented Using Nano-MOSFET by Analyzing Sub-Band Potential Energy Profile and Current-Voltage Characteristic of Quasi-Ballistic Transport ()

1. Introduction

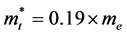

In traditional semiconductor devices, carriers are frequently scattered from phonons, ionized impurities and surface roughness. In the traditional devices, the backscattering mean free path λ is much shorter than the device channel. So, drift-diffusion approach is used to describe the carrier transport. However, as devices downscale to nanometer regime, backscattering mean free path become comparable to transistor dimensions. When the backscattering mean free path becomes much larger than the transistor channel length, scattering can be totally ignored. In this situation, a nano-MOSFET behaves like a vacuum tube. In practical devices, scatterings are unavoidable in semiconductor devices. Therefore, modern devices operate in quasi-ballistic mode which is between drift-diffusion and ballistic regimes. Put in other words, drift-diffusion theory is no longer strictly valid as well as ballistic treatment. Hence, modern device engineer must familiar with both approaches. Then, the nano-MOSFET studied in this paper is applied in implementing logical NOT transistor level circuit [1] [2] [3] [4] .

2. Theory and Methodology

Silicon (Si) MOSFETs currently operate between the ballistic and diffusive limits; the scattering model provides a conceptual model for transport in this quasi-ballistic regime. In this scattering model, the most important scatterings occur in the low-field region near the beginning of the channel at source side. Carrier scattering in the channel reduces the current and can be described by ballistic efficiency. Scattering model predicts that the drain current is close to the ballistic limit under high drain bias than under low drain bias, and the on-state current in strong inversion is limited by a small portion of the channel near the source, that is the top region of sub-band potential barrier.

The double-gate (DG) nano-MOSFET structure used in NanoMOS simulation is shown in Figure 1 with simulation structural parameters listed in Table 1.

![]()

Figure 1. Structural DG Nano-MOSFET used in nanoMOS simulation tool.

![]()

Table 1. Double gate nano-MOSFET device simulation parameter.

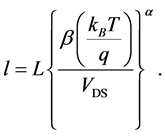

The on-state current of the nano-MOSFET is controlled by a short low-field region close to the source end of the channel. The length l of this area is called critical length which is defined as the distance from the peak of the potential barrier to the point

where the potential reduces by .

.  is a numerical factor ≥1. This factor has a

is a numerical factor ≥1. This factor has a

value of 1 for non-degenerate case and slightly greater than 1 for degenerate case. In this paper, take .

.  is the backscattering mean free path. Then, the backscattering coefficient r is given by

is the backscattering mean free path. Then, the backscattering coefficient r is given by

(1)

(1)

The ballistic efficiency B is given by

(2)

(2)

(3)

(3)

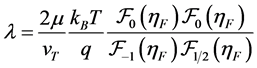

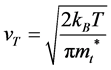

where electron mobility at ballistic transport in Silicon is  cm2/Vs. The thermal velocity is given by

cm2/Vs. The thermal velocity is given by

(4)

(4)

where  and T = 300 K. The critical length is given by

and T = 300 K. The critical length is given by

(5)

(5)

Since lower bound for  is used at diffusive transport and upper bound for

is used at diffusive transport and upper bound for  is used at ballistic transport,

is used at ballistic transport,  is used at quasi-ballistic transport.

is used at quasi-ballistic transport.

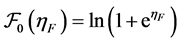

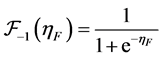

In studying the theoretical part of this paper, the following Fermi-Dirac integrals are used:

(6)

(6)

(7)

(7)

![]() (8)

(8)

where

![]() (9)

(9)

![]() is the average energy between source and drain in sub-band energy profile whereas

is the average energy between source and drain in sub-band energy profile whereas ![]() is the energy level at the center of the device. Next, the following expression is used to analyze the drain current per micron of width:

is the energy level at the center of the device. Next, the following expression is used to analyze the drain current per micron of width:

![]() (10)

(10)

After considering the ballistic efficiency B,

![]() (11)

(11)

![]() (12)

(12)

is the gate oxide capacitance per unit area

![]() (13)

(13)

![]() (14)

(14)

![]() is the average energy between source and drain in sub-band energy profile whereas

is the average energy between source and drain in sub-band energy profile whereas ![]() is the energy level at the region around top of the potential barrier. This region limits on-state current because scatterings mostly occur in this region. In analyzing Equation (10) and Equation (11), the following Fermi-Dirac integrals are used:

is the energy level at the region around top of the potential barrier. This region limits on-state current because scatterings mostly occur in this region. In analyzing Equation (10) and Equation (11), the following Fermi-Dirac integrals are used:

![]() (15)

(15)

![]() (16)

(16)

The on-line current-voltage (I-V) simulation result of NanoMOS is compared with theoretical calculation using Equation (11).

In order to calculate resistance RLoad of nano-MOSFET at quasi-ballistic limit, uses

![]() (17)

(17)

Since digital logic gates operate at linear portion of I-V curve. This RLoad is used in analyzing rise time of transistor loaded NOT gate circuit. On the other hand, the following expression is used to obtain on-state channel resistance Rchannel at on-state which is used in fall time analysis.

![]() (18)

(18)

![]() = electron mobility at ballistic = 1200 cm2/Vs.

= electron mobility at ballistic = 1200 cm2/Vs.

![]() = Oxide capacitance per unit area.

= Oxide capacitance per unit area.

Transistor loaded NOT gate as shown in Figure 2 is simulated using WinSpice. The simulated rise time and fall time extracted from timing diagram are compared with theoretical calculated rise time and fall time [5] - [11] .

Since the nano-MOSFET operates at quasi-ballistic condition:

![]()

![]()

![]()

![]()

![]()

From Figure 3,

![]()

![]()

![]()

Figure 2. Transistor loaded NOT gate circuit.

![]()

Figure 3. Capacitance models in nano-MOSFET device.

![]()

From [12] , subthreshold swing S = 75 mV/V and drain induced barrier lowering DIBL = 80 mV/dec. So, CG, CS and CD can be calculated.

Total Capacitance of NOT gate = Gate Capacitance + Source Capacitance + Drain Capacitance + Area Capacitance + Sidewall Capacitance.

Rise time constant ![]() gate total capacitance.

gate total capacitance.

Rise time![]() , it takes 6.1 times duration to pass logic 1 than logic 0 through an n-channel MOS pass-transistor.

, it takes 6.1 times duration to pass logic 1 than logic 0 through an n-channel MOS pass-transistor.

Fall time constant ![]() gate total capacitance.

gate total capacitance.

Fall time ![]()

Propagation delay ![]()

Maximum signal frequency ![]()

3. Results and Discussion

Figure 4 shows the energy sub-band profile along the channel for nano-MOSFET studied in this paper. Drain-to-source voltage, VDS lowers the sub-band potential at the drain side by 0.60 eV [13] [14] [15] .

From Equation (3), the backscattering mean free path is

![]()

From Equation (5), the critical length is

![]()

From Equation (1), the backscattering coefficient is

![]()

From Equation (2), the ballistic efficiency is

![]()

![]()

Figure 4. The sub-band energy profile along the channel for Nano-MOSFET.

In order to analyze the NanoMOS simulation result of Figure 5, Equation (10) and Equation (11) are needed. Take VDS = 0.60 V.

Then, by using Equation (10),

![]()

After considering the ballistic efficiency B and using Equation (11),

![]()

Simulated result with NanoMOS, as in Figure 5, has ![]() From theoretical calculation of Equation (11),

From theoretical calculation of Equation (11), ![]() These two results are

These two results are

87.3% closely matched. In Figure 5, drain current in saturation region is sloping because electron scattering is considered in Figure 5 and at high drain bias, scattering model in nano-MOSFET exhibits drain current closer to the ballistic limit than under low drain bias.

At region above threshold, the Fermi-Dirac integrals in Equation (11) can be simplified to exponential terms as in equation below.

![]() (19)

(19)

Sub-band potential at drain side is lower by![]() , therefore

, therefore

![]()

Then Equation (19) becomes

![]()

Figure 5. Drain current versus drain voltage for nano-MOSFET by NanoMOS simulation.

![]() (20)

(20)

After analysis, Equation (19) and Equation (20) both has the same value.

![]()

To implement transistor level NOT gate circuit as in Figure 2, the nano-MOSFET should operate in the linear region which is the region for digital logic operation. From Figure 5, linear region is from VDS = 0.00 V until 0.20 V. Use Equation (11) to calculate the drain current at this linear region and then apply Equation (17) to calculate RLoad at quasi-ballistic limit. From Equation (11),

![]()

In order to calculate the resistance of nano-MOSFET at quasi-ballistic limit, use Equation (17) since digital logic gates operate at linear portion of I-V curve. Using Vth =

0.20 V, ![]() and from device dimension W = 125 nm, RLoad = 748.8

and from device dimension W = 125 nm, RLoad = 748.8

Ω. The resistance value is used in analyzing theoretical value of rise time in NOT gate circuit. On the other hand Equation (18) is used to obtain the resistance needed in analyzing theoretical value of fall time in NOT gate circuit. Finally, the NOT gate circuit in Figure 2 is simulated using WinSpice. The timing diagram result are shown in Figure 6(a) and Figure 6(b).

Low output voltage VOL of NOT transistor level circuit in Figure 2 is given by

![]() (21)

(21)

From WinSpice simulation timing diagram Figure 6(b),

![]() (22)

(22)

By comparing Equation (21) and Equation (22),

![]()

From theoretical modeling and also WinSpice simulation, VOH = 0.4 V. Nano- MOSFET at the bottom is at off state and thereby at high impedance state. Threshold voltage lost 0.20 V occurs at top side nano-MOSFET load which acts as pass transistor.

Table 2 tabulates the result of this investigation. The theoretical and simulated result are almost matched each other.

4. Conclusion

Modern MOSFET semiconductor devices operate in quasi-ballistic transport. Quasi- ballistic transport is the carrier transport between drift-diffusion and ballistic regimes.

![]() (a)

(a)![]() (b)

(b)

Figure 6. (a). WinSpice input signal with period 8 ps to NOT gate; (b) WinSpice output signal of NOT gate.

![]()

Table 2. Theoretical and simulated result comparison table.

Theoretical calculations and simulation results about this transport have been done in this paper and this paper shows that theoretical calculation values and simulation results are closely matched. Logic NOT circuit level has been implemented using nano- MOSFET and correct logical operation has been achieved.