# Study and Implementation of the Bit-Error Test Method for Burst-Mode Optical Signal

#### SHI Wei, HUANG Qiuyuan

School of Information Engineering, Wuhan University of Technology, Wuhan, China

**Abstract:** On the basis of the characteristic of TDMA uplink optical signal of PON system, this article puts forward a method of high-speed optical burst bit-error rate testing based on FPGA. The article proposes a new method of generating the burst signal pattern include user-defined pattern and pseudo-random pattern, realizes the slip synchronization, self-synchronization of error detection using data decomposition technique and the traditional irrigation code synchronization technology, completes high-speed burst signal clock synchronization using the rapid synchronization technology of phase-locked loop delay in the external circuit and finishes the bit-error rate test of high-speed burst optical signal.

**Keywords:** burst mode optical signal; bit error test; fixed-point logic compare; synchronization

# 突发光信号误码测试方法的研究与实现

施 伟,黄秋元

武汉理工大学信息工程学院,武汉,中国,430070

摘 要:针对 PON 系统的上行 TDMA 光信号特点提出了基于 FPGA 的高速突发光信号误码测试比对方法。提出了新的高速突发人工码元的产生方法,实现了人工自定义码型与伪随机码结合的突发信号码型;采用了数据分解技术与传统灌码同步技术相结合,实现了各支路同步、误码检测自同步;在外围电路中采用延时锁相环的快速同步技术,完成了高速突发信号时钟同步。实现了高速突发光信号的误码测试。

关键词: 突发光信号; 误码测试; 定点比对; 同步

#### 1 前言

随着通信技术的不断发展, PON 系统广泛应用于 宽带接入技术。在 PON 系统中, 上行信号的传输方式 是 TDMA 方式, 光 TDMA 信号具有突发信号特点: 各个时隙的信号幅度大小不均衡,相位不均衡,有长 "0"长"1"的出现。这与连续的光信号有很大的不同,决 定了光 TDMA 的帧结构中,前置码用于电平恢复,不 同数据包之间相位存在跳变。一般采用连续信号的误 码等效测试的方法,但在 GPON 的 TDMA 信号包间隔 很小的情况下,连续信号的误码等效测试的方法,需 要一套专门的测试系统,来检测突发光接收模块的误 码性能。突发误码仪的码型产生和码型比对方法与连 续误码仪有很大不同。在连续信号的测试中,传输的 数据都可以当作有效码元,所以在比对的时候,直接 将接收的数据直接比对。但是在突发误码测试时中, 根据突发信号的特点,需要进行电平恢复和比特位的 同步,并且需要快速同步。

本文的主要工作是提出了基于 FPGA 的突发光信号产生方案,在接收端提供进行码型比对和定位误码检测方法,并在 FPGA 中完成了代码设计,实现了高速突发光信号的误码测试。

#### 2 突发光信号误码测试原理及要求

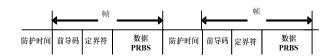

帧包括帧头和数据两部分,帧头标志帧的起始位置,数据是需要传输的有效码元,帧和帧之间还有帧间隔。根据 PON 系统的上行信号特点和包结构的定义,如图 1 所示。

图 1. PON 系统的上行帧结构

帧头中的前导码中有一部分是用来幅度恢复的, 并且在幅度恢复的数据比特期间,允许有误码的出现, 误码的比对只针对定界符后的数据;另外因为数据包

之间的相位跳变,在每一个数据包到来时,接收到定界符之前需要提取同步信息。这就需要产生一种符合 突发信号特点的光信号,并且产生符合图 1 要求的帧数据。在进行误码比对时,防护时间、前导码、数据包,以及 CID 的插入等长度都需要可变的定位比对。

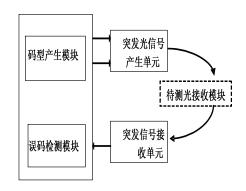

PON 系统的上行帧结构测试系统的总体方案如图 2 所示。

图 2. 发光信号误码测试原理图

通过可编程逻辑门阵列 (FPGA)产生两路符合图 1 帧结构的突发电信号,经突发光信号产生单元产生突发光信号。突发光信号接收单元可以从接收到的信号中分离出这两路信号,送往误码检测模块进行同步误码比对从而对光突发传输系统(即上行系统)中的各种光器件的性能,特别是突发模式工作的光接收模块的突发误码特性进行测试。本文中主要是为这样一个测试提供一种产生突发模式的信号源以及进行突发数据同步误码比对的方法。

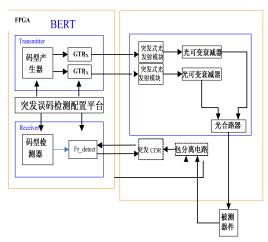

图 3. 光信号误码测试方案设计图

# 3 突发光信号误码测试方案设计

系统采用FPGA实现了人工自定义码型与伪随机码

结合的突发信号码型,经数据分离 GTP 通道产生两路高速突发人工码元,由突发光模块(SFF)形成两路光信号,再经不同的光可变衰减器、光合路器,形成突发光信号。在接收端首先通过突发式光接收模块转换成相应电信号,采用高速"与"电路实现相应帧的选择,在外围电路中采用延时锁相环(CDR)的快速同步技术,完成了高速突发信号时钟同步。最后在 FPGA 内部采用传统灌码同步技术实现误码比对。该系统如图 3 所示。

## 4 突发光信号误码测试具体实现方法

据突发光信号误码测试整体方案设计,其功能模块主要包括码型产生和码型检测两部分。

#### 4.1 码型产生部分

#### 4.1.1 突发数据帧的产生方法

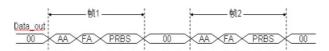

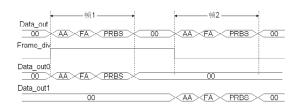

在测试系统中,码型产生器需要产生两路周期包模式的数据(data\_out0 和 data\_out1),在发明中采用一路信号(data\_out)由分离信号分成两路信号(data\_out0 和 data\_out1)的方法来获得这两路信号。产生一路具有上面所述帧格式的数据 data\_out。生成数据的示意图如图 4。

图 4. ata\_out 数据示意图

图中 00 代表帧间隔,AA 代表前导码,FA 代表定界符,前导码和定界符又合称为帧头;PRBS 代表发送的是伪随机码,也就是帧数据。帧1和帧2交替发送。

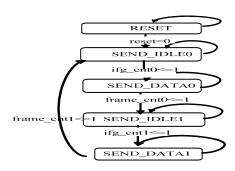

要产生 data\_out 信号,需要用到图 5 所示的状态机机制。

- (1)RESET,复位状态。如果 reset=1,继续保持 RESET 状态;如果 reset=0,则进入 SEND\_IDLE0 状态。

- (2)SEND\_IDLEO。当处于此状态时,data\_out 发送的数据包含帧 2 后帧 1 前的间隔(00),帧 1 的前导码(AA),帧 1 的定界符(FA)。Ifg\_cnt0 是一个递减的计数器,它的初值等于帧 1 的空闲的长度,并且data\_out 每发送一位帧 1 的空闲数据,它的值减 1。当ifg\_cnt0>1 时,仍然处于 SEND\_IDLEO 状态,当ifg\_cnt0<=1 时,进入下一状态(SEND\_DATAO)。

- (3)SEND\_DATAO。当处于此状态时,data\_out 发送的数据是伪随机码,也就是帧中的有效码元。 Frame\_cntO 是一个递减的计数器,它的初值等于帧 1 的帧数据的长度,并且每发送一位帧数据,它的值减 1。

当 frame\_cnt0>1 时,仍然处于 SEND\_DATA0 状态, 当 frame\_cnt0<=1 时,进入 SEND\_IDLE1 状态状态。

(4)SEND\_IDLE1。当处于此状态时,data\_out 发送的数据包含帧 1 和帧 2 的间隔(00),帧 2 的前导码(AA),帧 2 的定界符(FA)。Ifg\_cnt1 是一个递减的计数器,它的初值等于帧 2 的空闲的长度,并且 data\_out每发送一位帧 2 的空闲数据,它的值减 1。当 ifg\_cnt0>1时,仍然处于 SEND\_IDLE1 状态,当 ifg\_cnt0<=1时,进入下一状态(SEND\_DATA1)。

图 5. 型发生器的状态机设计

(5)SEND\_DATA1。当处于此状态时,data\_out 发送的数据是伪随机码,也就是帧中的有效码元。Frame\_cnt1 是一个递减的计数器,它的初值等于帧 2的帧数据的长度,并且每发送一位帧数据,它的值减 1。当 frame\_cnt1>1 时,仍然处于 SEND\_DATA1 状态,当 frame\_cnt0<=1 时,进入 SEND\_IDLE0 状态,以此类推,从而产生帧 1 和帧 2 交替出现的帧数据。

#### 4.1.2 接收帧的选取方法

要分离出这两种帧信号,可以用 data\_out 分别与控制信号"frame\_div"以及控制信号的取反信号"~frame\_div"进行"与"操作来分离出这两路信号。

即: Data\_out0=Data\_out&frame\_div

Data\_out1=Data\_out&~frame\_div

在这里,产生 frame\_div 信号的思路是在每个帧的 交汇处产生一个跳变的时钟信号。如图 6 所示:

图 6. 输出数据的示意图

#### 4.2 码型检测部分

误码检测部分包含两个要点,一个是接收码型的

同步方法, 二是接收到的数据的比对方法。

#### 4.2.1 同步方法

#### ① 码元同步方法

码元同步主要是使接收到的数据和接收的时钟同步。这个过程可以在 FPGA 外部的突发信号接收单元通过专用突发 CDR 芯片实现。

图 7. 收 CDR 电路工作示意图

时钟数据恢复(CDR) 电路可以从接收到的含有较大干扰和抖动的数字信号中提取接收位同步时钟,并用这个时钟对该数据信号重新采样,恢复出具有规范波形的原数据信号。恢复出的时钟与恢复出的数据已经达到同步,可以作为误码检测模块的数据和时钟输入。

在每一帧的数据到来时,只有利用一部分数据(一般是前导码)通过时钟数据恢复电路恢复出稳定的时钟后,才进行后面的数据比对。由于产生的突发测试信号的帧的格式是:

- A: 44bit 前导码(默认,长度可调)

- B: 20bit 定界符 (默认,长度可调)

- C: 包间隔: 8\*N(N为不为0的任意值)

- D:包长度:8\*M(M为不为0的任意值)

只有在 44bit 前导码内恢复出稳定的时钟, 才不会影响后面数据的比对。所以根据设计的要求选择相应的 CDR 才是关键。

#### ②有效数据的起始定位方法

这部分的的任务就是要找出每一帧中帧数据(有效数据)的起始位置。这里采用的是在帧中(帧数据前)插入特定的定位比特,从而在接收部分扫描出这些特殊的定位比特来找到帧数据的起始位置的方法。这些定位比特就是前面所说的定界符。

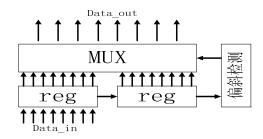

为了实现有效数据的起始定位,误码检测模块应该包含一个字边界检测模块,其功能是从接收到的数据中检测出定界符,确定帧数据的边界,从而达到有效数据的起始定位的目的,这是误码比对可以正确进行的先决条件。字边界检测模块的结构如图 8 所示。

可编程误码仪发送的每一个数据包都以44bit的前导码和 20bit 的定界符 1010111111010111111010 (AFAFA)开头,且除了这20bit外,任意一段内都不准出现1010111111010111111010。

当有 20bit10101111101011111010 通过电路时, 经

过特殊设计的字边界检测模块就输出一高电平,产生 帧头信号。

图 8. 边界检测模块的结构图

此模块的构建思想是:将数据放入寄存器(reg)进行缓冲,在缓冲的数据中寻找定界符以确定bit的偏移位数,根据此参数可以确定有效数据的起始位置,并从该位置开始数据的操作,从而达到帧同步的目的。

#### 4.2.2 比对方法

#### ① 比对机制

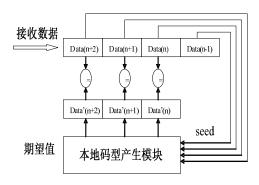

接收到了发送的伪随机码后,如何得到原始的信号与接收到的伪随机码进行误码比对就是接收模块的关键。之前的方法一般是采用发射的原始信号作为比对信号,但是发射和接收到的信号的延时难以控制,这是突发误码比对首先要解决的问题。

在本发明中,采用的是自同步误码检测机制,即从接收到的伪随机码中提取本地码型产生器所需的状态量,用来恢复出原始伪随机码作为本地码,与接收到的数据进行比对。这种方法可以进行远距离误码测试。原理图如图 9 所示:

图 9. 同步比对机制的原理图

图中,本地码型产生模块包含在误码检测模块内部,是一个和码型产生模块一样的模块。Data(n+2),Data(n+1),Data(n),Data(n-1)是几个周期内依次接收到的信号,Data'(n+2),Data'(n+1),Data'(n)是用接收到的信号作 SEED 值并由本地误码检测模块产生的数据(伪随机码是由 SEED 值计算出来的)。

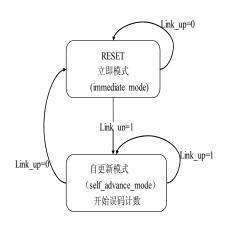

比对机制的是如图 10 所示状态机来实现。图中 link up 指示连接状态,具体工作流程如下:

图 10. 对机制的状态图

A 复位后,本地码型产生模块工作在立即模式,即使用接收到的数据作为 SEED 值产生期望数据来和接收到的码型进行比对,如果连续 r 个 (可设定)时钟周期内数据没有误码,则认为 link\_up=1,进入下一状态(自更新模式);反之则继续工作在立即模式。

B 在自更新模式下,本地码型产生模块不再把接收数据作为 SEED 值,而是把自己产生的数据来作为更新数据的 SEED 值。在这种模式下,仍然把期望值与接收数据进行比对,并开始启动误码计数器,开始进行误码计数。

C 如果连续 r 个时钟周期内检测到误码,则认为 link\_up=0,则回到立即模式,重新进行自同步检测; 否则仍然工作在自更新模式。

#### ②比对点设置

突发信号的比对跟连续信号有很大不同,在突发误码仪中,码型是以帧为基本单位传输的。帧一般可分为帧头和数据两部分,帧和帧之间还有帧间隔。帧间隔没有任何数据,不需要进行误码比对;帧数据是需要进行误码比对的部分;并且根据待测器件的指标,帧头中需要比对的位置也是不确定的(取决于对帧头中有效数据的位数的要求)。

针对突发信号的特点,本发明根据上面提出的帧数据格式提供了突发信号的比对方法,即从接收到的每帧数据中,提取出一部分进行比对,比对的起点设置为前导码中的某位(可以设置),比对的终点设置为帧数据的终点。为了确定每帧数据比对的边界,可以通过下面步骤来实现。

A 通过字边界检测电路扫描出帧数据边界的起始 位置。

- B 通过帧数据边界的位置计算出要比对的起始点的位置(该点的位置在前导码中,具体根据用户的设置而定)。

- C 通过计数器找到每帧数据的结尾,作为比对的 终点位置。

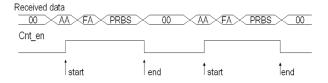

- D 产生一个控制误码计数器计数的信号 cnt\_en,步骤 B 和步骤 C 计算出的起点和终点作为 cnt\_en 信号的跳变沿。在每帧比对数据的边界内, cnt\_en 为高电平,其余时刻 cnt\_en 为低电平。

E 通过 cnt\_en 的状态控制误码计数器的工作,当 cnt\_en 为高电平时,误码计数器正常工作,每比对出一个误码,计数器的值加 1; 当 cnt\_en 为低电平时,误码计数器的值保持不变。

这样,比对边界以外的时间内,虽然有误码比对,但是误码计数器的值不增加,相当于没有计算那部分时间的误码。

具体工作的示意图如图11所示:

图 11. 收比对示意图

当 cnt\_en 为高电平时,误码计数器才进行计数,cnt\_en 为低电平时,误码计数器的值保持不变。起始点(start)和终点(end)表示误码比对的起始点和终点。

#### 5 结论

本课题能够较好的模拟 PON 系统中传输信号的特点,为突发光信号的测试系统提供测试所需的码型以及测试的方法。采用本课题提出的方法能够真实的反应出待测器件的性能,并且本课题提出的方法均能在FPGA 内部通过可编程逻辑进行验证并实现。采用本课题所提供的方法能够大大提升测试系统的性能。

噪比代价与前导码和保护时间的变化关系。同样, 由图 6 可以看出,前导码增加或保护带增加,均会减 小信噪比代价,即增加了信噪比。

### References (参考文献)

- Yamada.Y, Mino.S, Habara K. "Ultra-fast clock recovery for burst-mode optical packet communication". Optical Fiber Communication Conference and the International Conference on Integrated Optics and Optical Fiber Communications. 1999, Page(s): 114-116.

- [2] P. Ossieur, Y.C. YI, J. Bauwelinck, et al. DC-coupled 1.25 Gbit/s burst-mode receiver with automatic offset compensation[J]. ELEC-TRONICS LETTERS. 2004, VOL.40, NO.7, Page(s):447-448.

- [3] P. Ossieur, T. D. Ridder, Xing-Zhi Qiu, et al. Influence of Random DC Offsets on Burst-Mode Receiver Sensitivity. Journal of Lightwave Technology. 2006, VOL.24, Page(s):1543-1550..

- 4] Quan Le, Sang-Gug Lee, Yong-Hun Oh. "Burst-mode receiver for 1.25Gb/s Ethernet PON with AGC and internally created reset signal". 2004 IEEE International Solid-State Circuits Conference. 2004, Page(s):474-540.

- [5] Roo-Da Lee, Hyun-Kyun Choi, Ho-Yong Kang. "An implement of clock phase alignment for burst-mode data recovery in GPON". International Conference on Optical Internet held jointly with the 32nd Australian Conference on Optical Fibre Technology. 2007, Page(s):367-369.

- [6] "Design and Simulation of the AC-coupled Burst-mode optical receiver with a large time constant", Proceeding of Asia Pacific Optical Communications conference (APOC2008), 2008.10.

- [7] "Design and Simulation of the AC-coupled Burst-mode optical receiver with the small time constant", Proceeding of Photonics and OptoElectronics Meetings (POEM2008), 2008.11.